# CS 110 Computer Architecture Datapath

Instructors: Siting Liu & Chundong Wang

Course website: https://toast-

lab.sist.shanghaitech.edu.cn/courses/CS110@ShanghaiTech/Spring-2024/index.html School of Information Science and Technology (SIST) ShanghaiTech University

2024/4/9

## Administratives

- Lab 6 available.

- HW 3 ddl April 9th today!

- Proj1.1 will be checked next week

- Proj1.2 ddl April 25th

- Proj2.1 will be released soon

- Discussion (teaching center 301) schedule

- Datapath for proj 2.1

- The same content for Friday and the next Monday.

# Mid-term I

- Midterm I

- April 11th 8:00 am 10:00 am

- We start sharp at 8:00 am!

- Arrive 7:45 am to check-in (three classrooms likely and seat table will be determined on-site)

- Arrive later then 8:30 am will get 0 mark.

- Contents:

- Everything till April 9th lecture

- Switch cell phones off!!! (not silent mode)

- Put them in your bags.

- Bags in the front. On the table: nothing but pen, exam paper, 1 drink, 1 snack, your student ID card and your cheat sheet!

- One of teaching center 301/304/404, check on-site

# Mid-term I requirements

- You can bring a cheatsheet (handwritten only). 1-page A4, double-sided (2-page for the mid-term II and 3-page for the final). Put it on your desk at exam. Cheatsheet that does not apply to the rules would be taken away.

- <u>Greencard</u> shown on the course website is provided with the exam paper.

- No other electronic devices are allowed!

- No ear plugs, music, smartwatch, calculator, computer...

- Anybody touching any electronic device will **FAIL** the course!

- Anybody found cheating (copy your neighbors answers, additional material, ...) will **FAIL** the course!

# Cheat Sheet

- 1 A4 Cheat Sheet allowed (double sided)

- Midterm II: 2 pages

- Final: 3 pages

- Rules:

- <u>Hand-written</u> <u>not printed/photocopied!</u>

- Your **<u>name</u>** in pinyin on the top!

- Cheat Sheets not complying to this rule will be <u>confiscated</u>!

# Outline

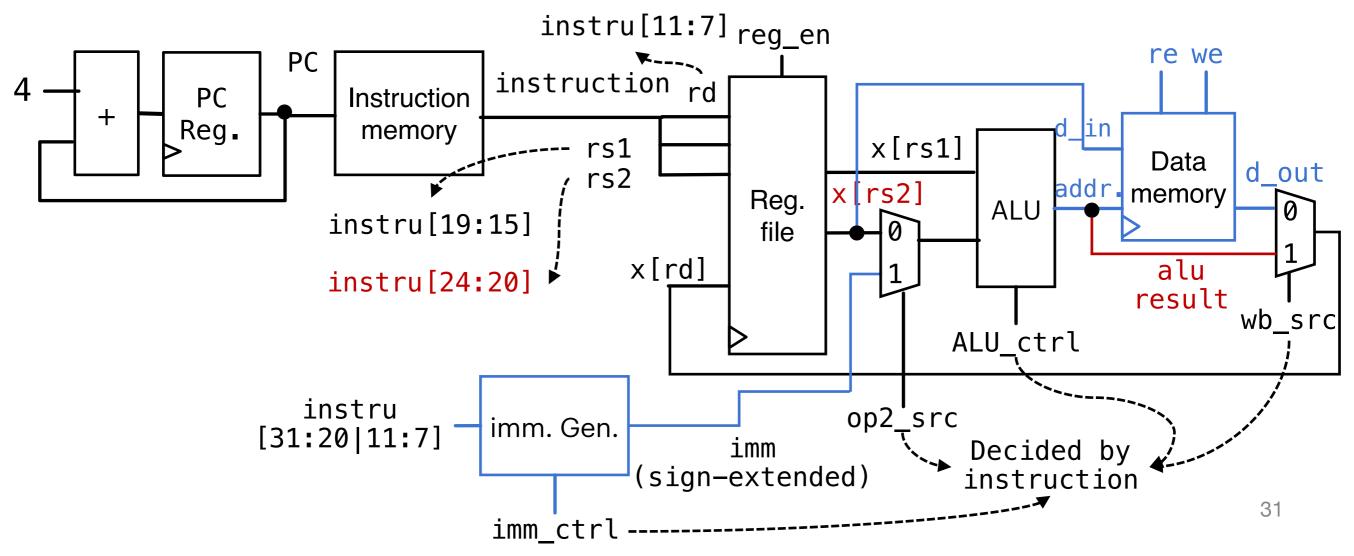

- Datapath

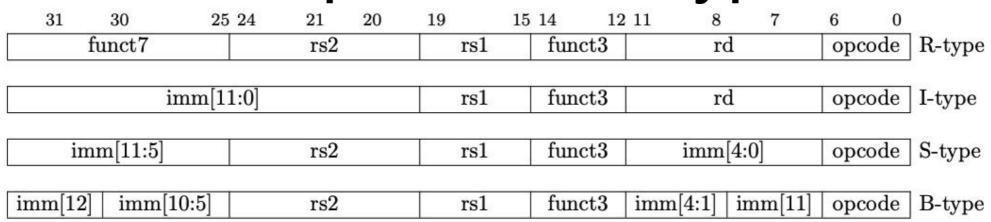

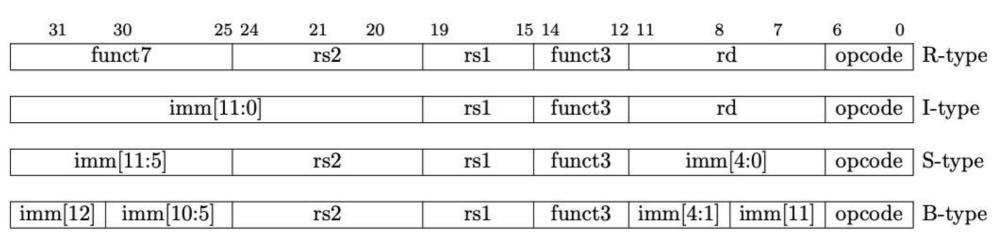

- Add building blocks and control signals for different types of instructions, one type at a time

- Design of the controller

- Timing analysis

# **Controller & Datapath**

A CPU that support RV32I can have so many states

- Consider the 32 registers alone

- x0 always 0

- Each bit in the other registers can be 0 or 1

- Not practical to enumerate all the state transitions

- Top-down design: build small modules and then connect them as needed

- Most digital systems can be divided into datapth and controller

- Datapath contains data processing and storage

- Controller controls data flow and state change (still can be modeled as FSM)

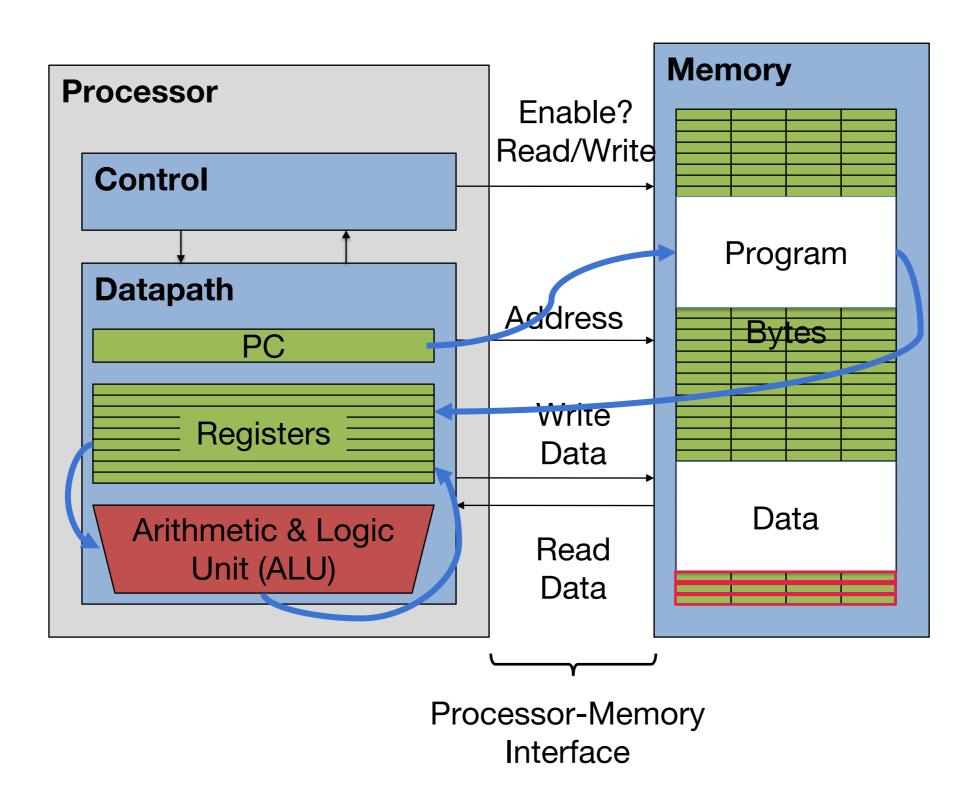

- Recall the execution of an instruction

- Our Goal: Implement a RISC-V processor as a synchronous digital system (SDS).

- Each RV32I instruction can be done within 1 clock cycle (single-cycle CPU).

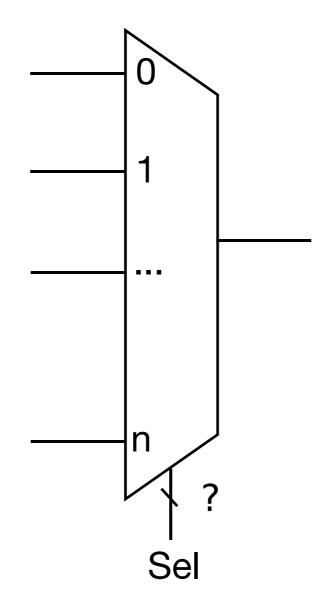

## Multiplexer

• n-to-1 multiplexer symbol

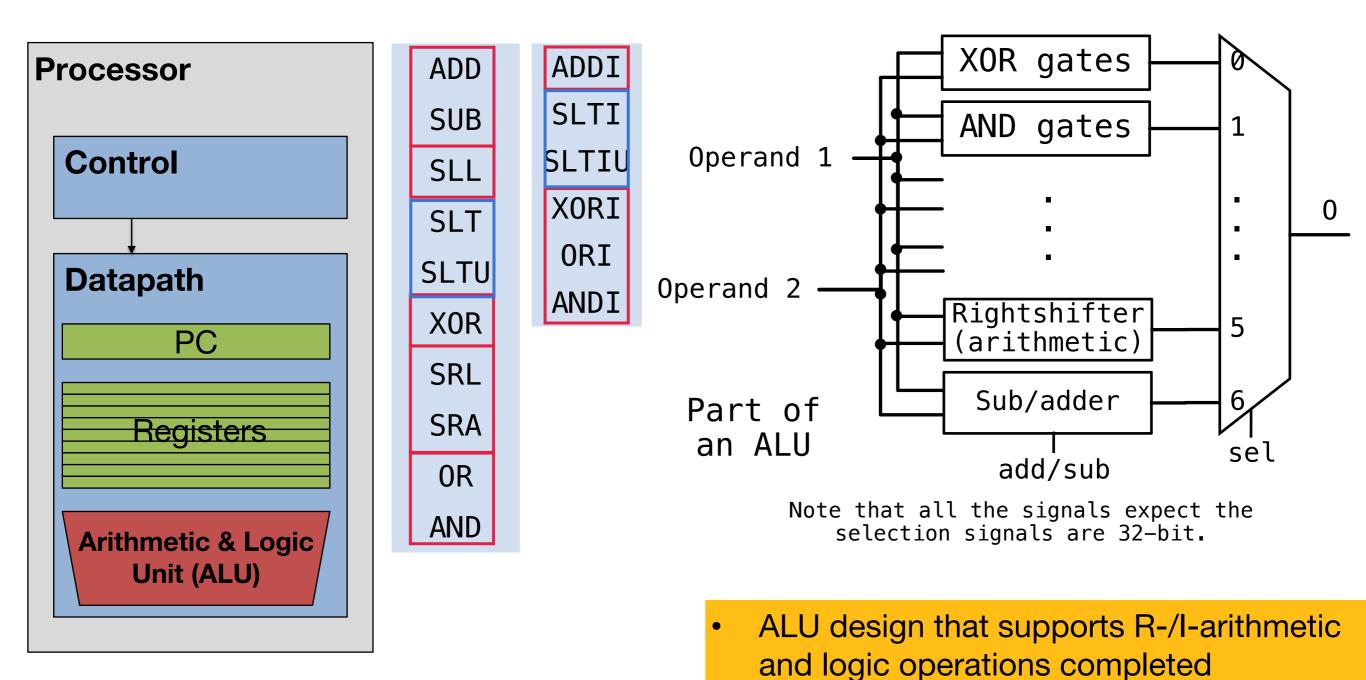

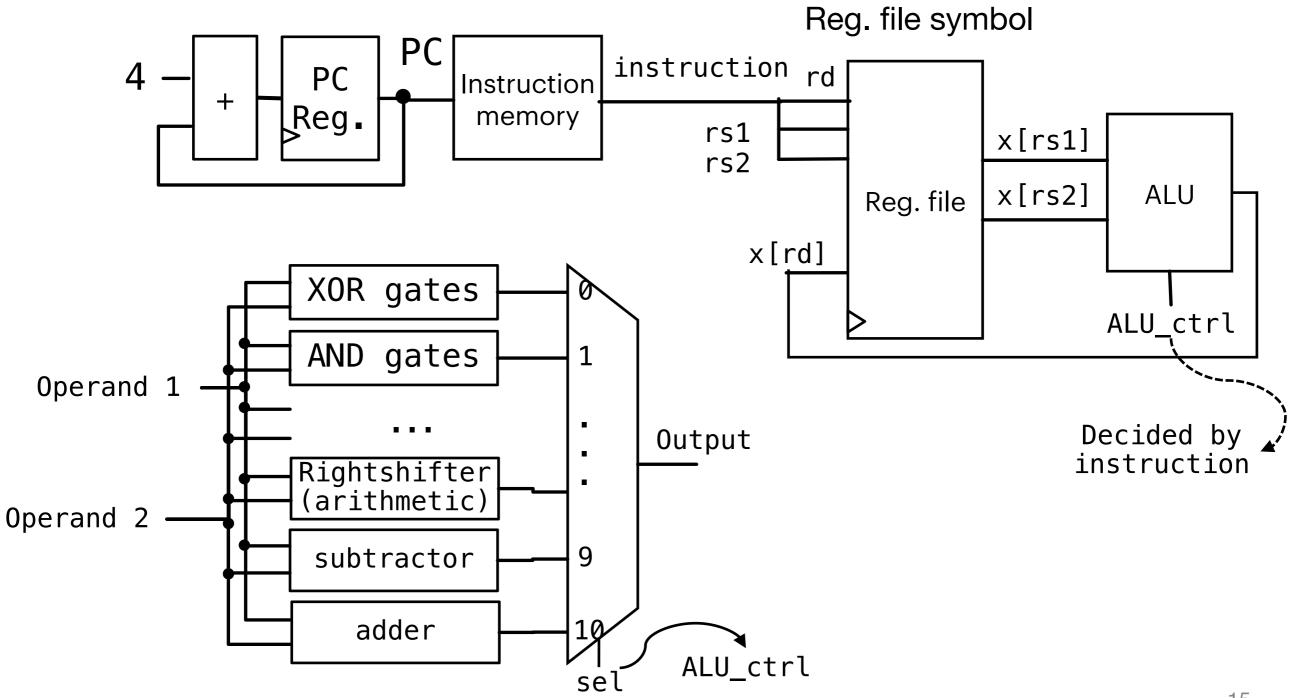

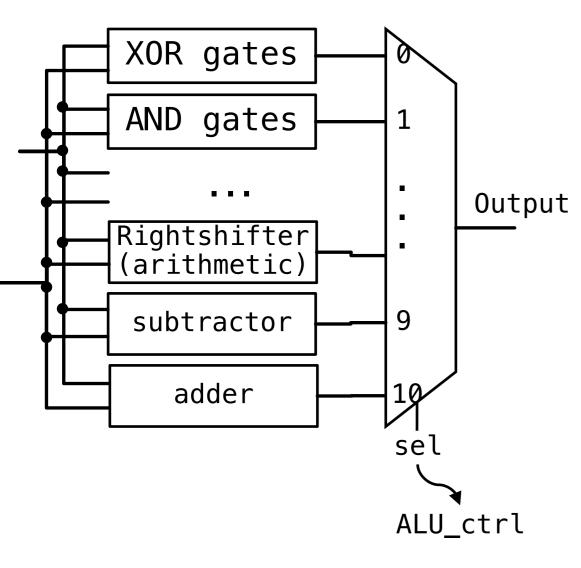

# ALU

• An ALU should be able to execute all the arithmetic and logic operations

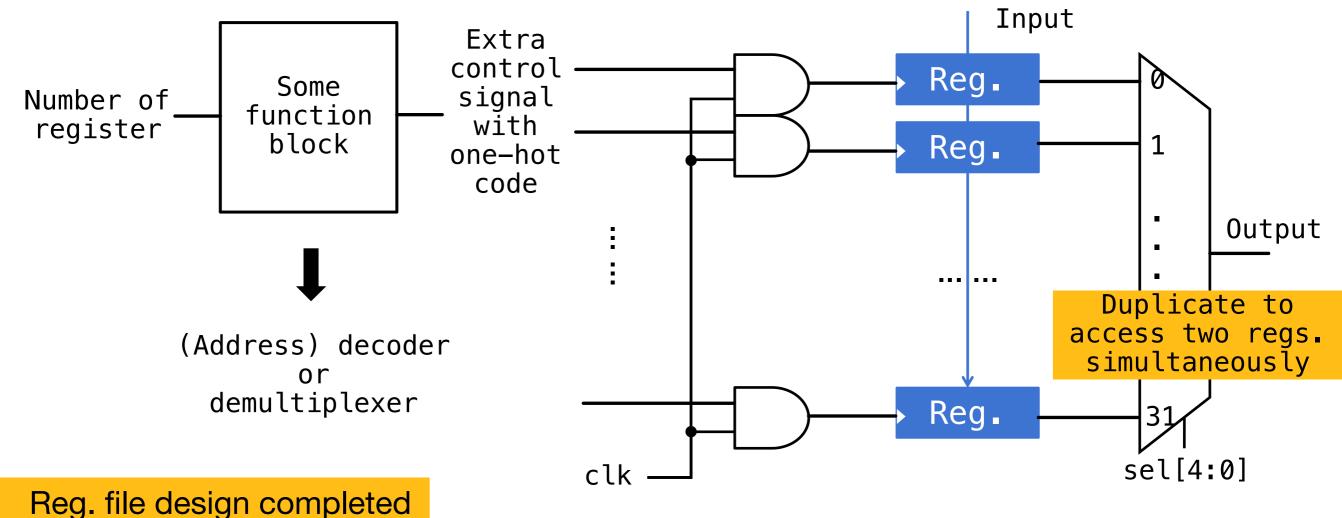

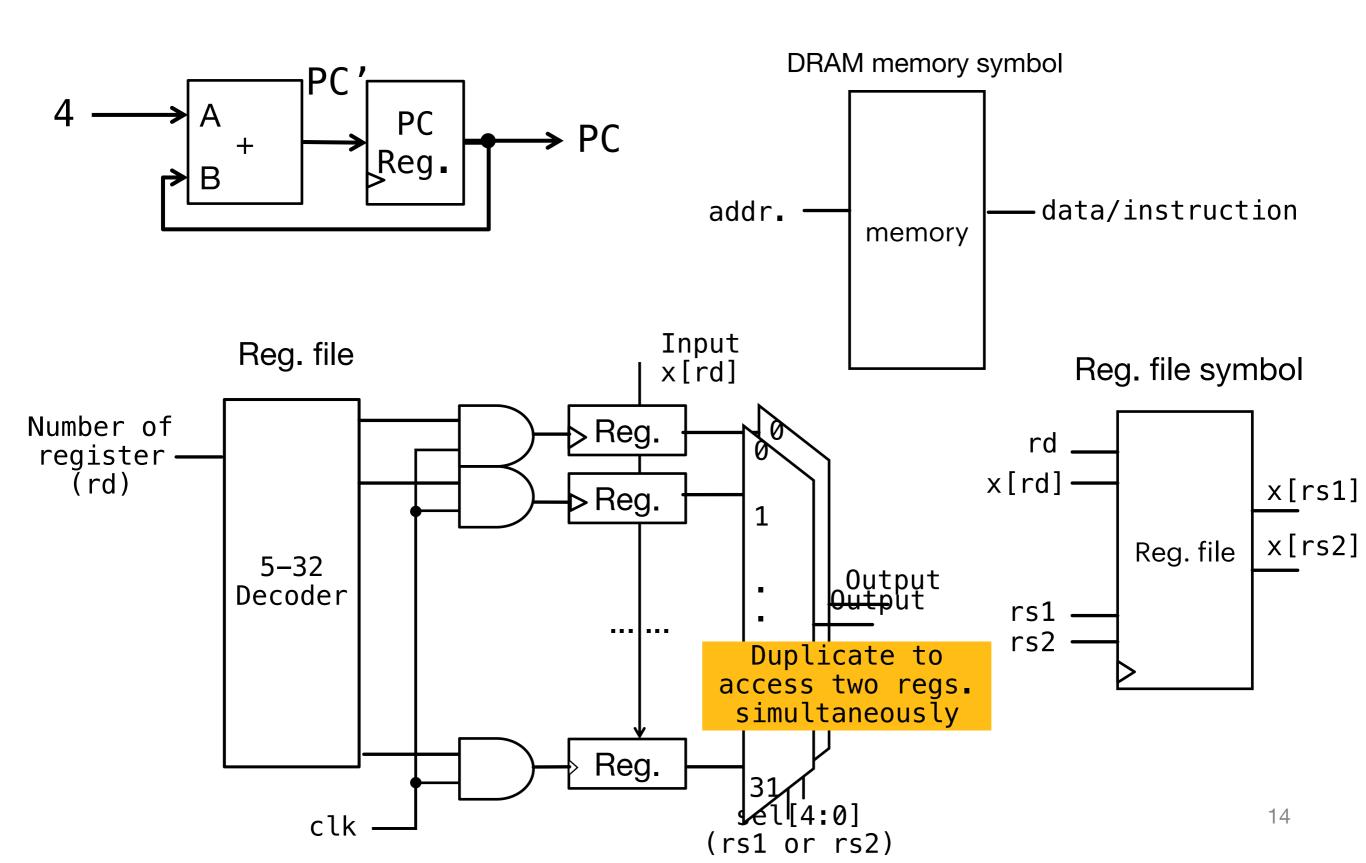

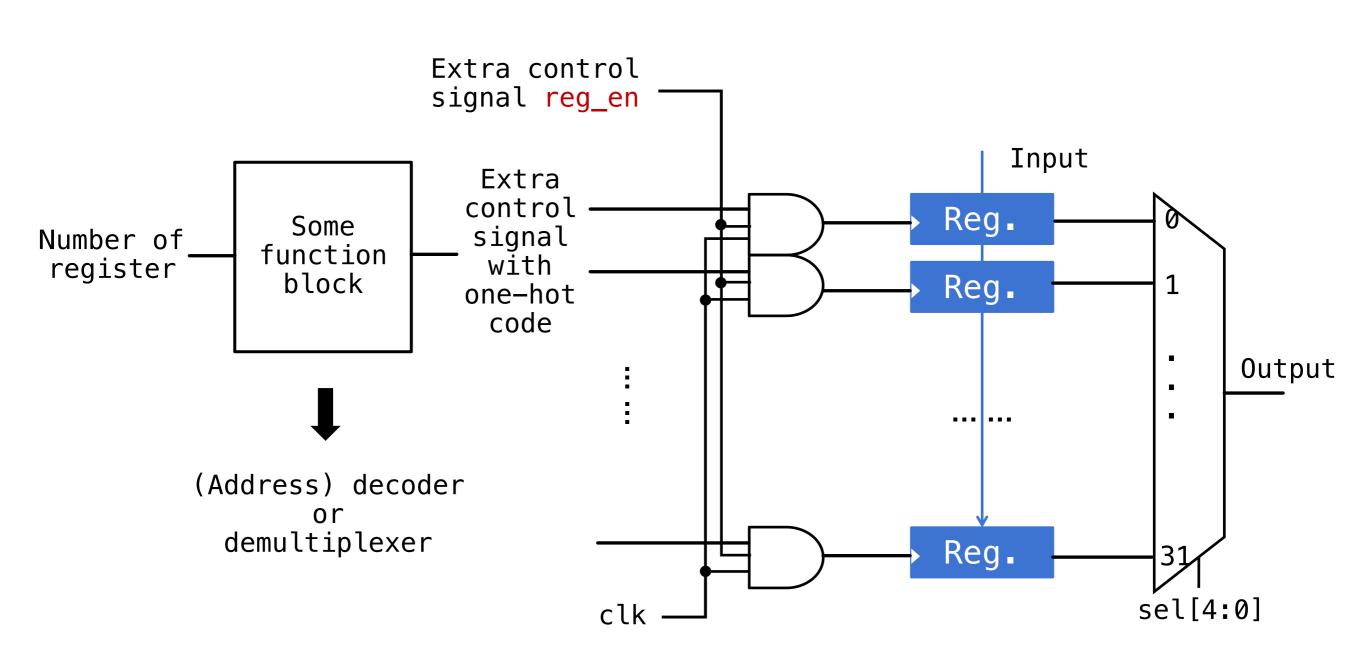

## Register file

- The register file is the component that contains all the general purpose registers of the microprocessor

- A register file should provide data given the register numbers

- A register file should be able to change the stored value

How do we change values of a specific reg.?

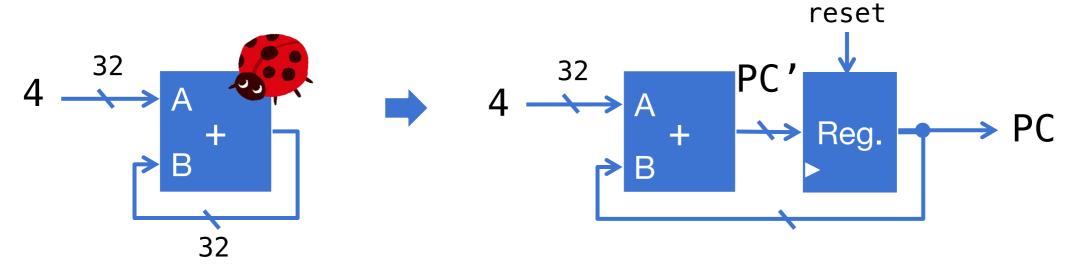

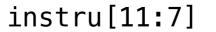

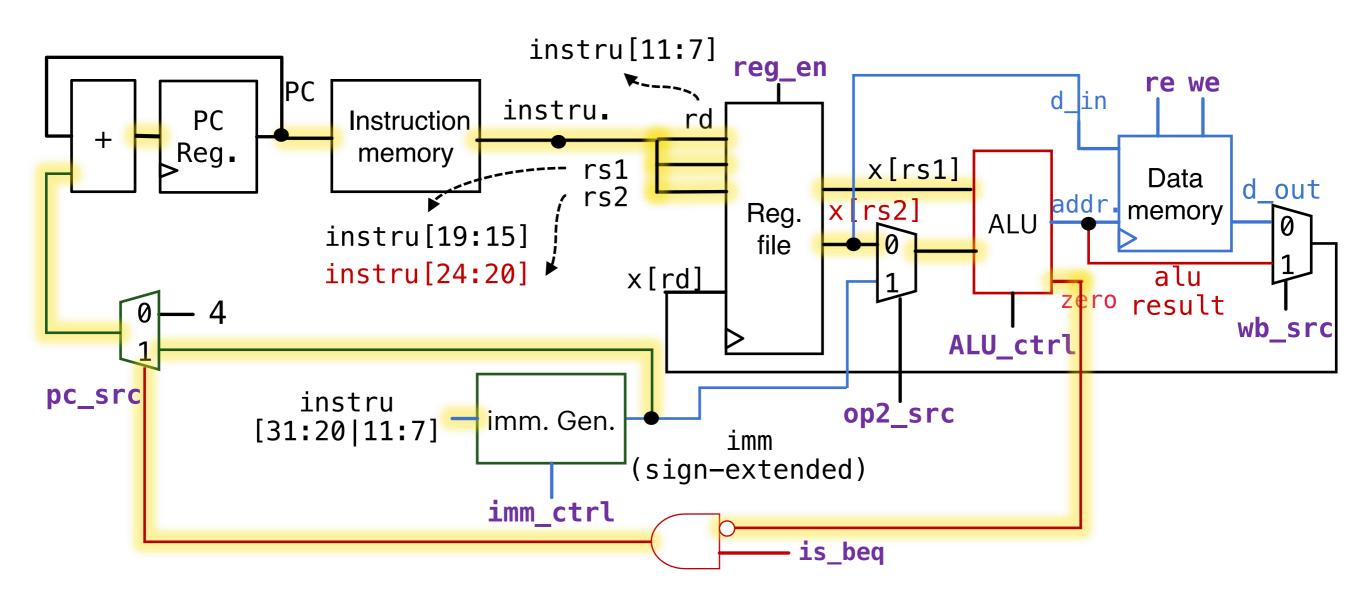

#### Datapath

#### We have covered PC register previously

- Synchronous digital circuit can have feedback, e.g., iterative accumulator

- e.g. PC = PC + 4 without considering branch or jump

• Timing diagram

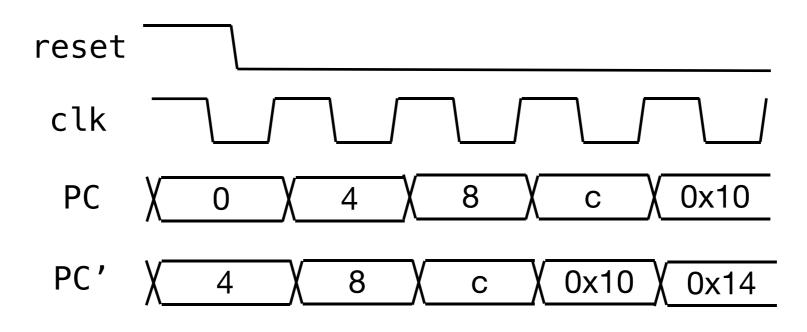

# Useful building blocks-Memory

- Memory similar to register file except that the basic cell design is different

- Requires refresh for DRAM

- For ease of implementation, we only use its behavior model

#### Datapath

#### Datapath

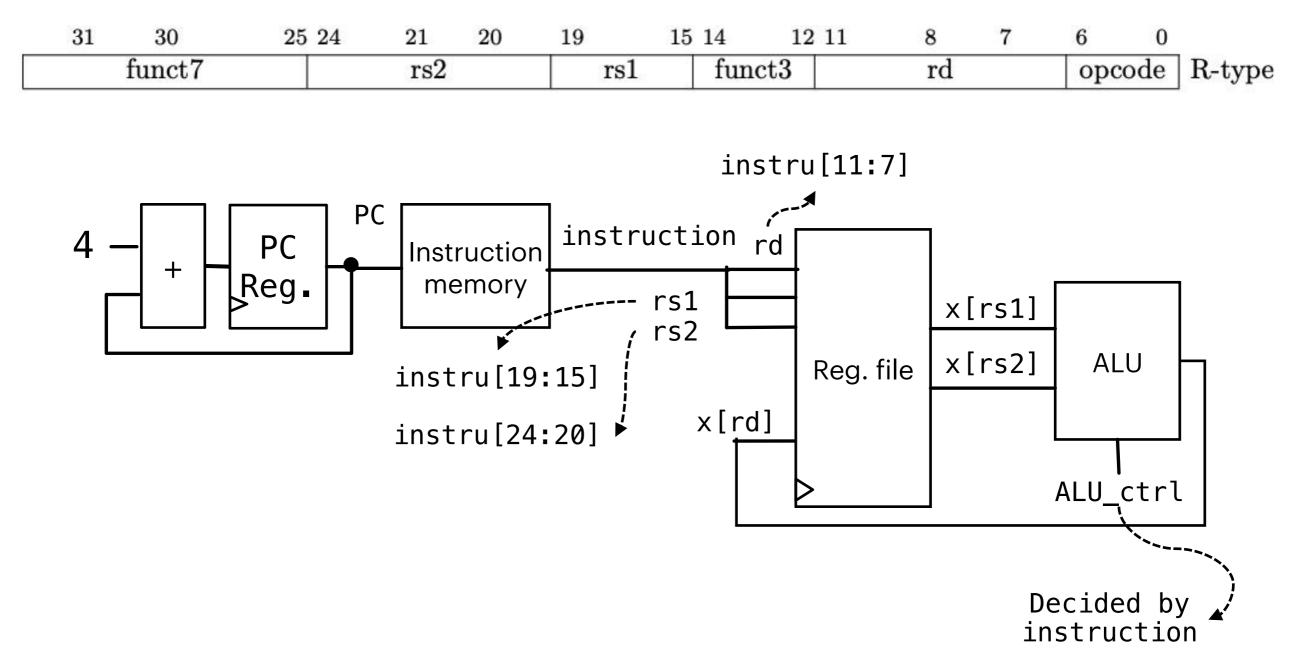

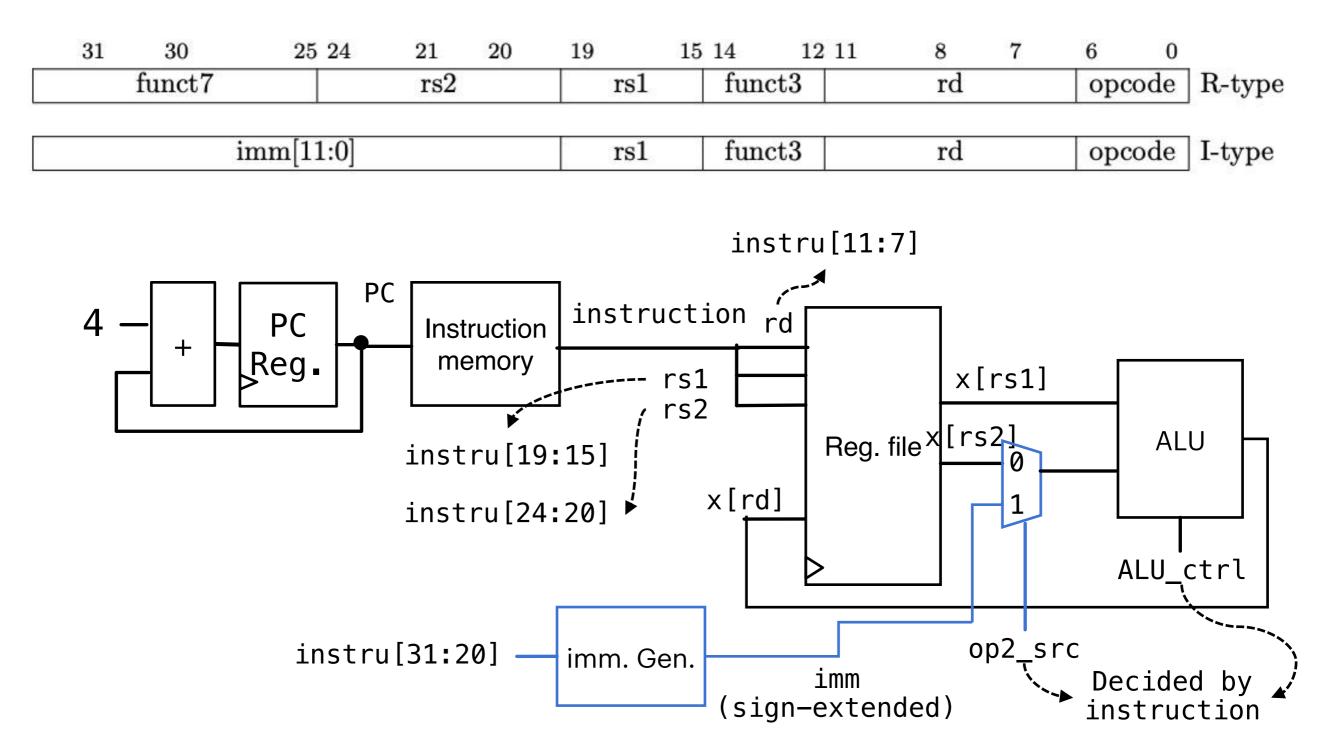

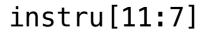

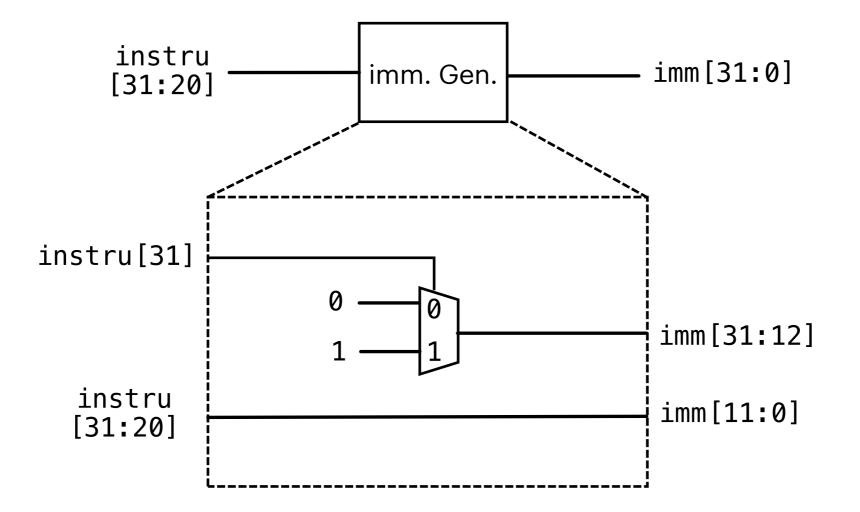

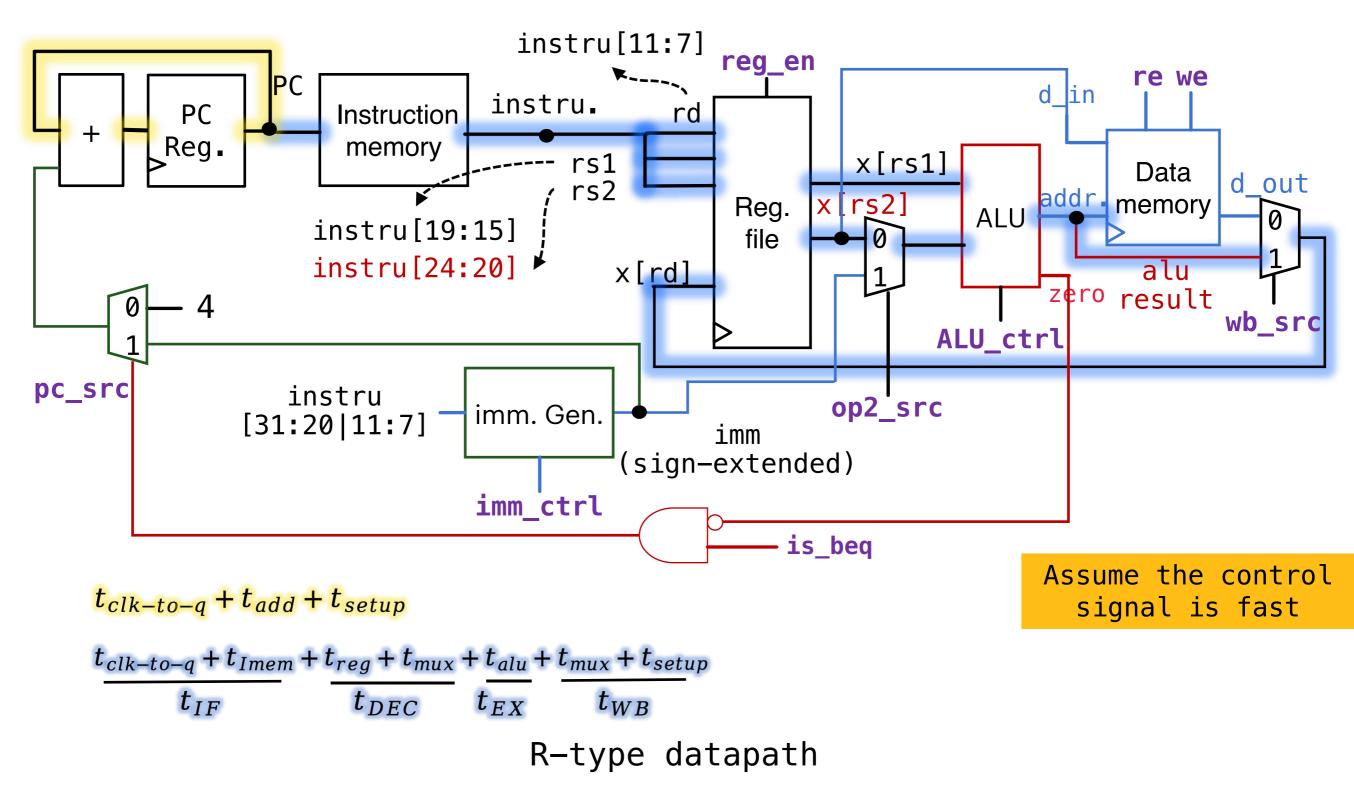

• We have all the building blocks to execute R-type instructions

• We have all the building blocks to execute R-type instructions

| 0000000 | rs2 | rs1 | 000 | rd | 0110011 | ADD  |

|---------|-----|-----|-----|----|---------|------|

| 0100000 | rs2 | rs1 | 000 | rd | 0110011 | SUB  |

| 0000000 | rs2 | rs1 | 001 | rd | 0110011 | SLL  |

| 0000000 | rs2 | rs1 | 010 | rd | 0110011 | SLT  |

| 0000000 | rs2 | rs1 | 011 | rd | 0110011 | SLTU |

| 0000000 | rs2 | rs1 | 100 | rd | 0110011 | XOR  |

| 0000000 | rs2 | rs1 | 101 | rd | 0110011 | SRL  |

| 0100000 | rs2 | rs1 | 101 | rd | 0110011 | SRA  |

| 0000000 | rs2 | rs1 | 110 | rd | 0110011 | 0R   |

| 0000000 | rs2 | rs1 | 111 | rd | 0110011 | AND  |

• We have all the building blocks to execute R-type instructions

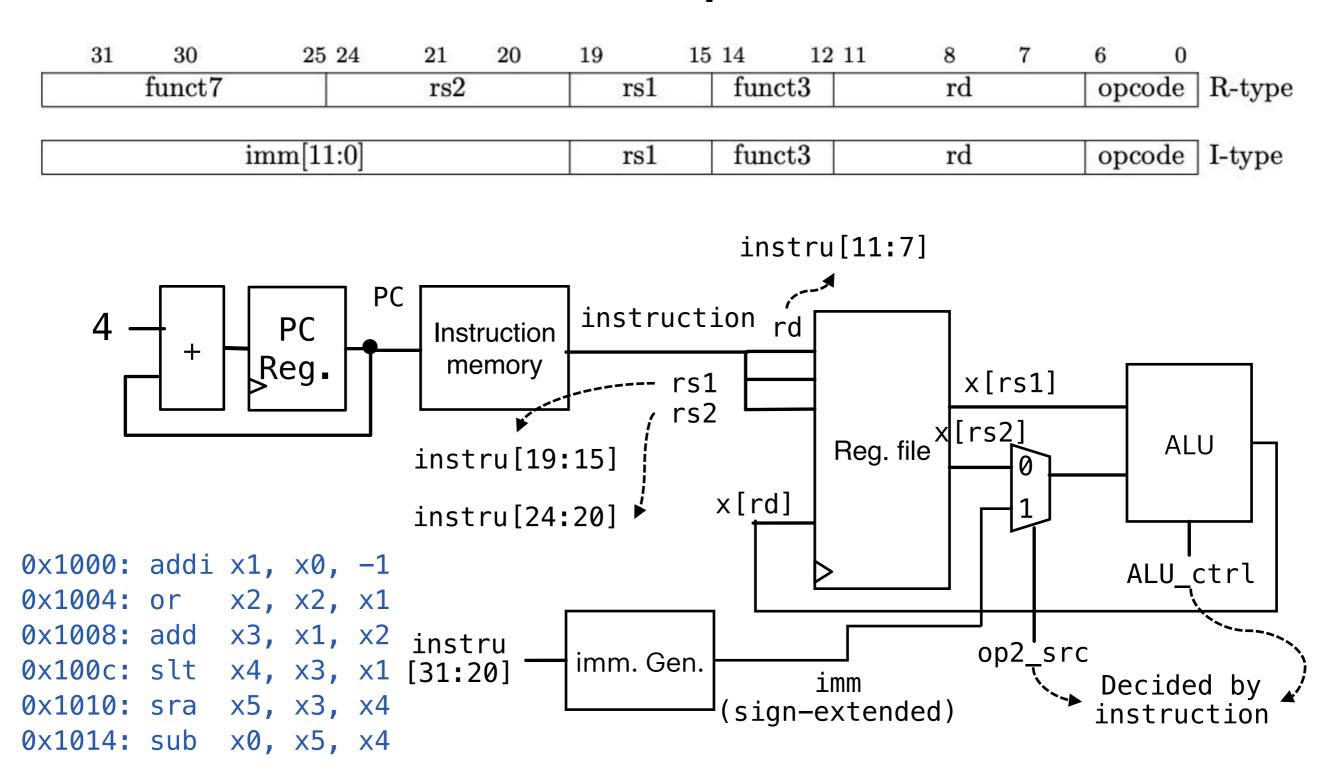

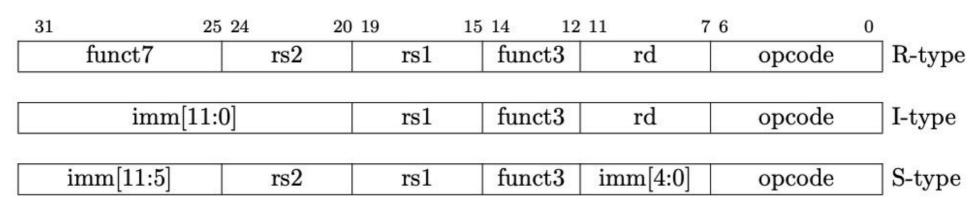

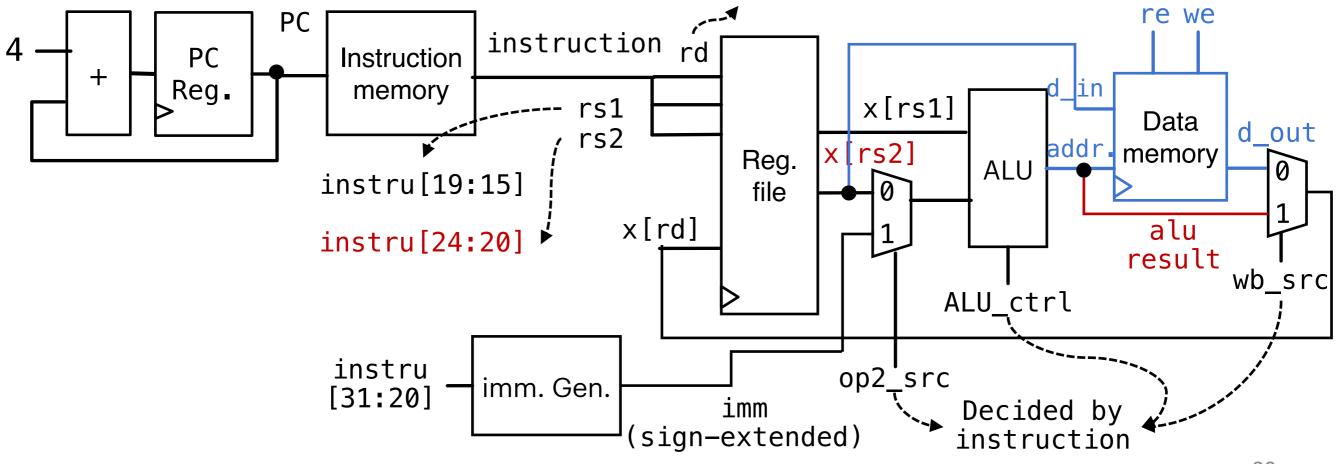

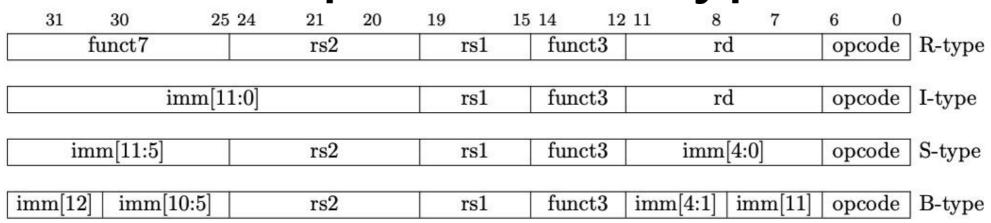

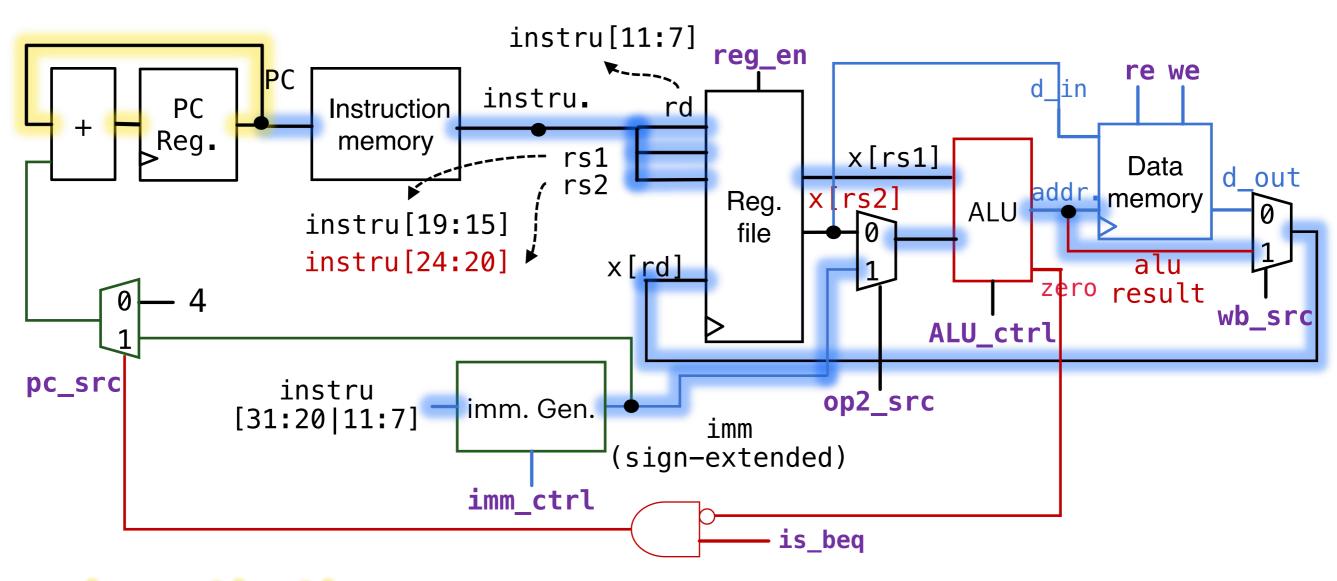

#### Datapath for I-type arithmetic and logic

#### Example

## Datapath for more types ...

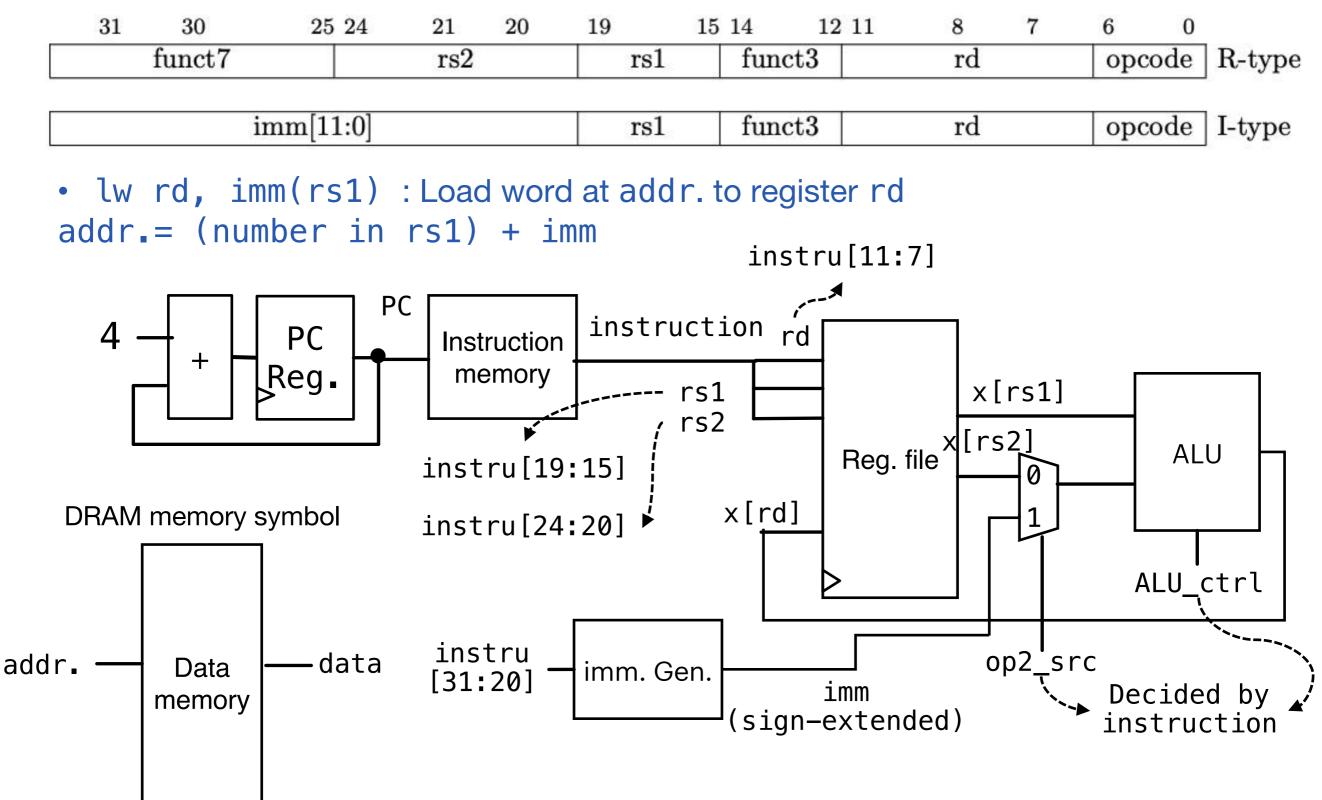

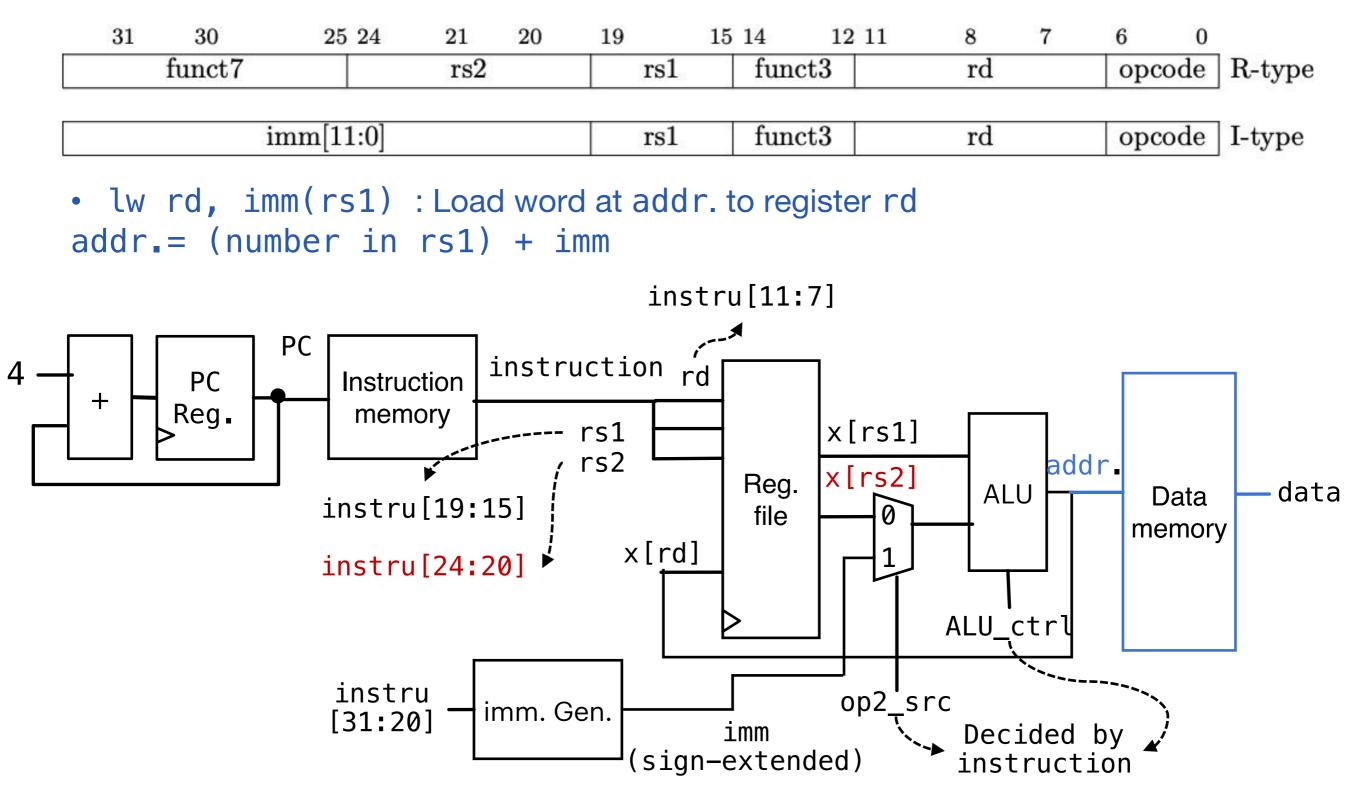

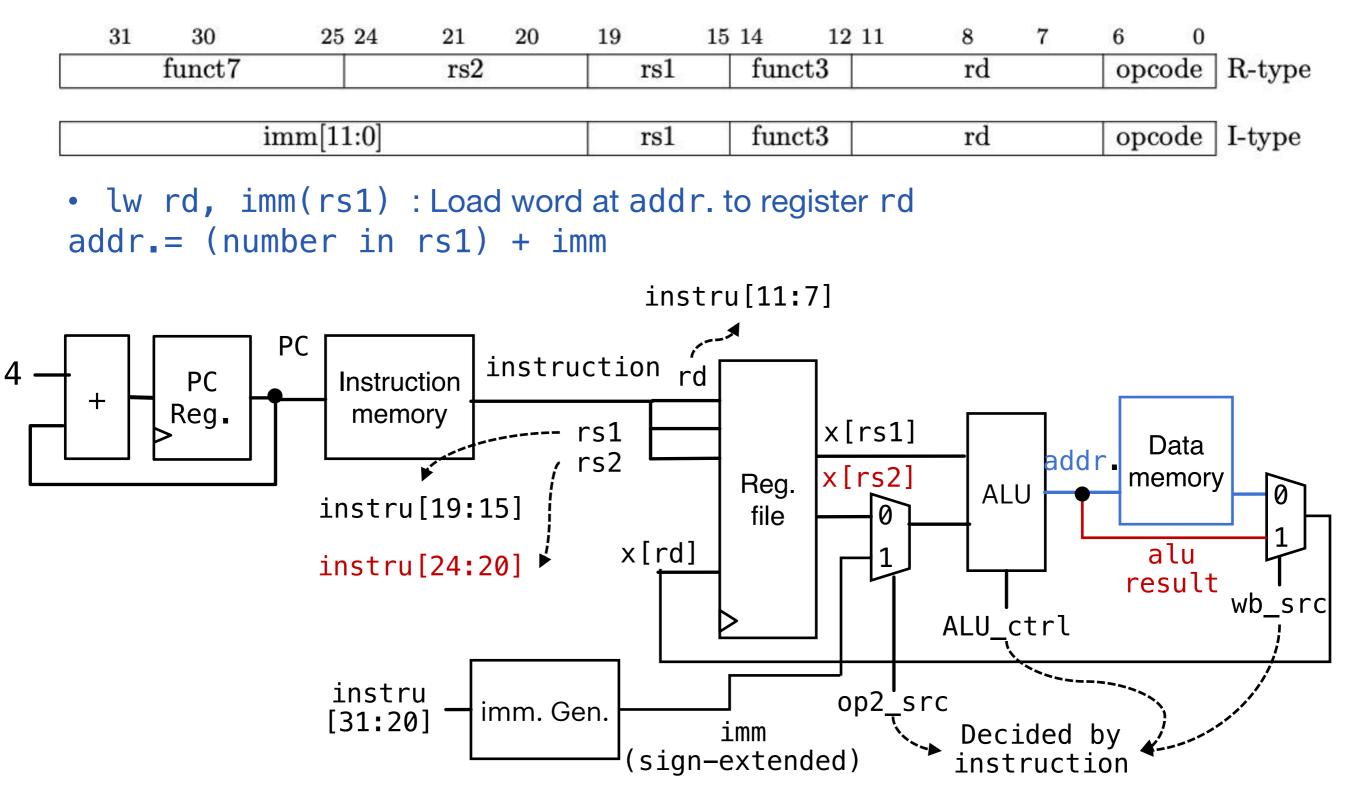

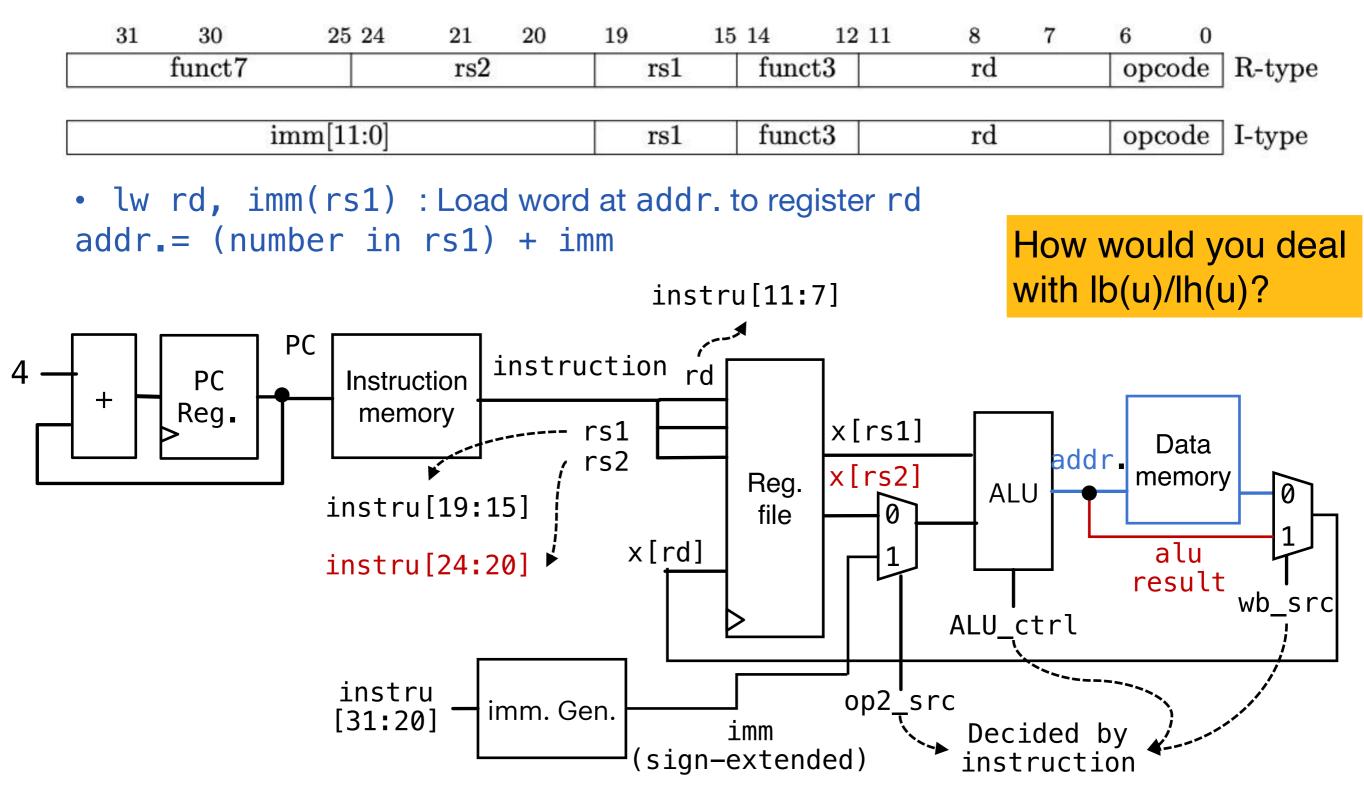

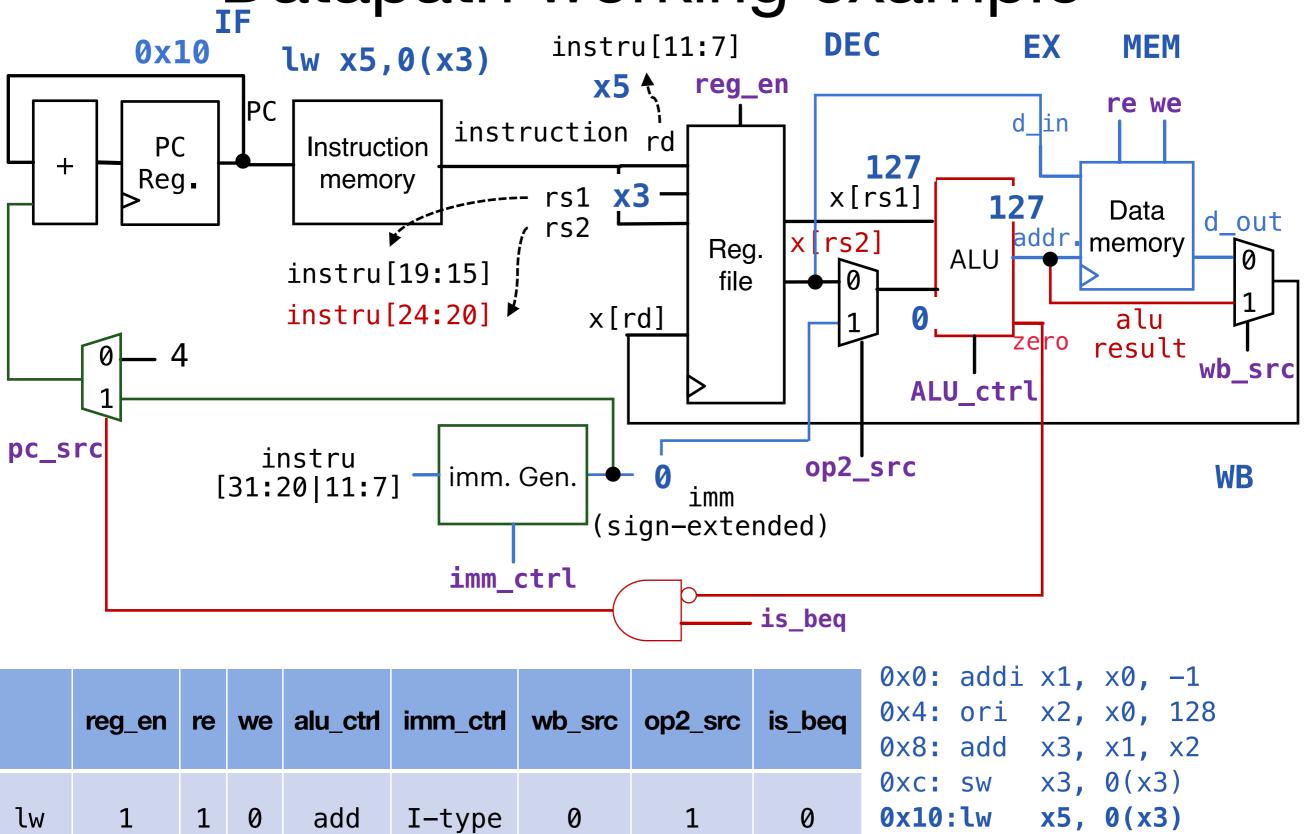

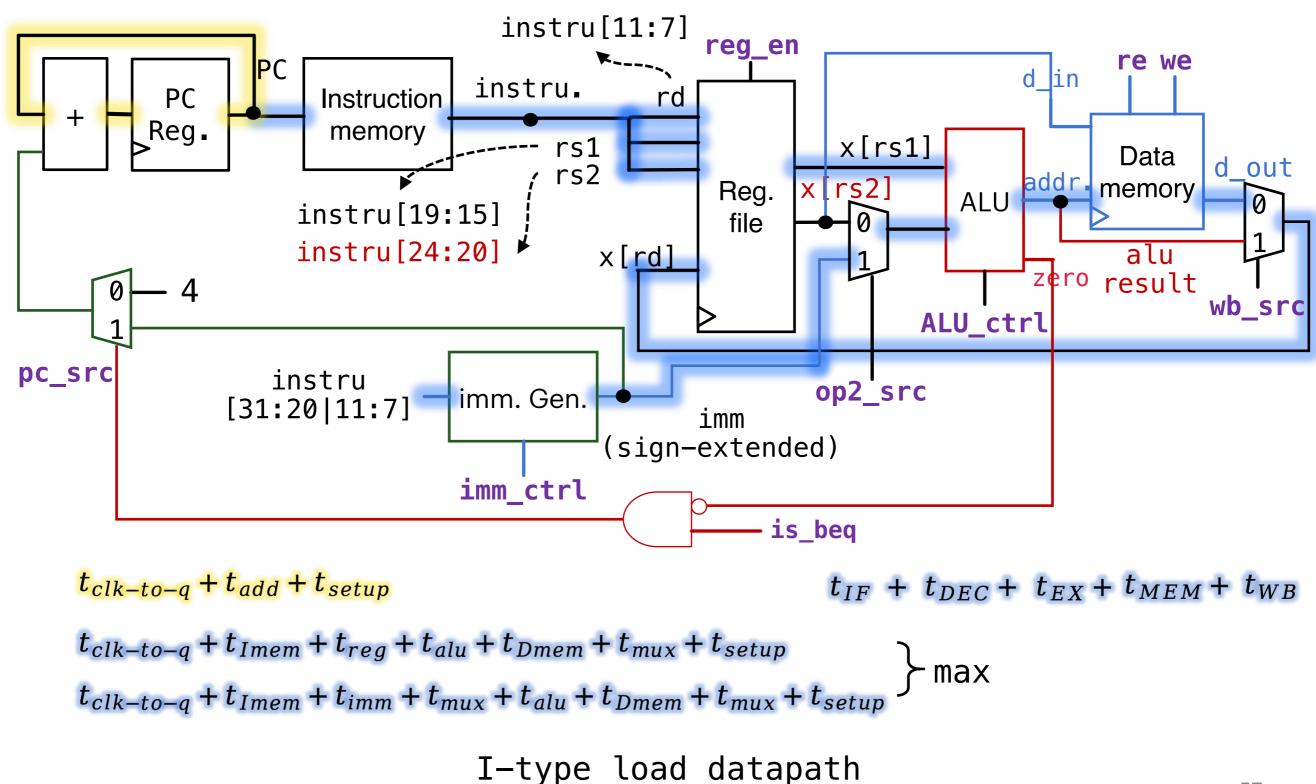

## Datapath for I-type load

## Datapath for I-type load

## Datapath for I-type load

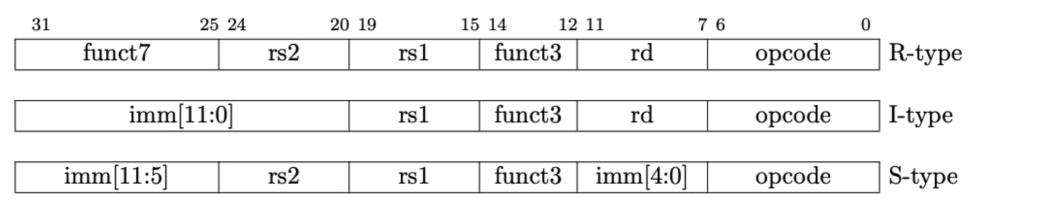

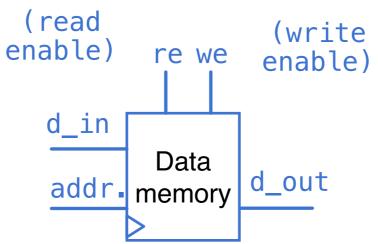

- Recall that in an FSM, only when there is a trigger (clk edge), the state can change.

- We assume that the change of data memory (memory-write) is also governed by clk edge.

- Assume behavior model of data memory:

- When we=1 && re=0, at clk rising edge, data[addr.]=d\_in; d\_out stays at high-resistance (output nothing)

- When we=re=0, d\_out stay at high-resistance (output nothing, state would not change); we=re=1 is forbidden

- When we=0 && re=1, d\_out=data[addr.]

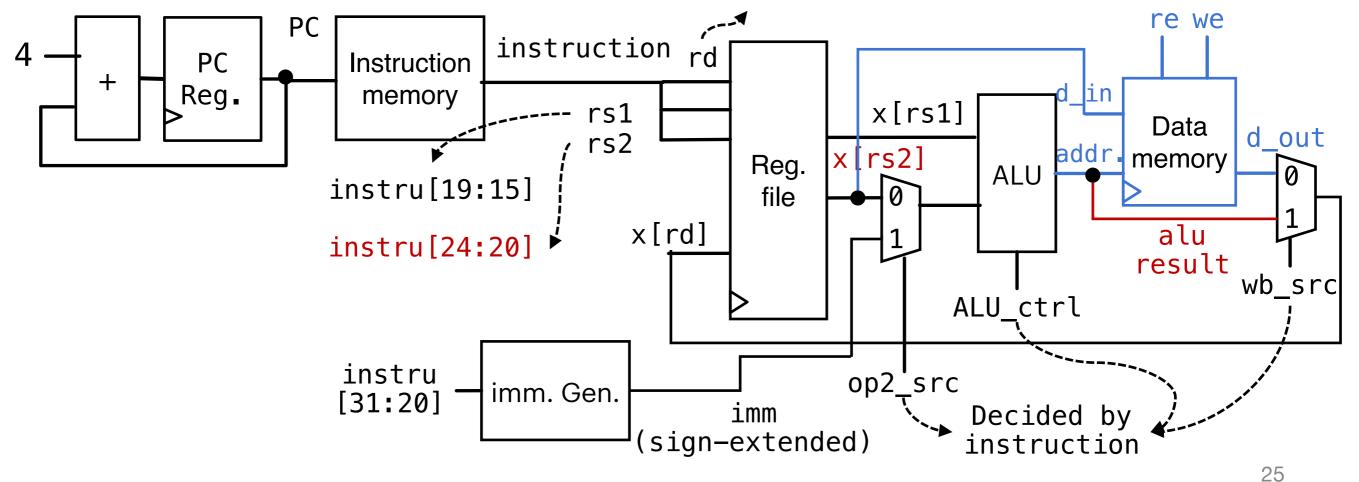

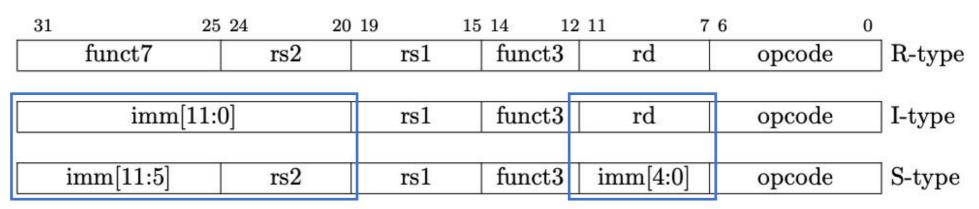

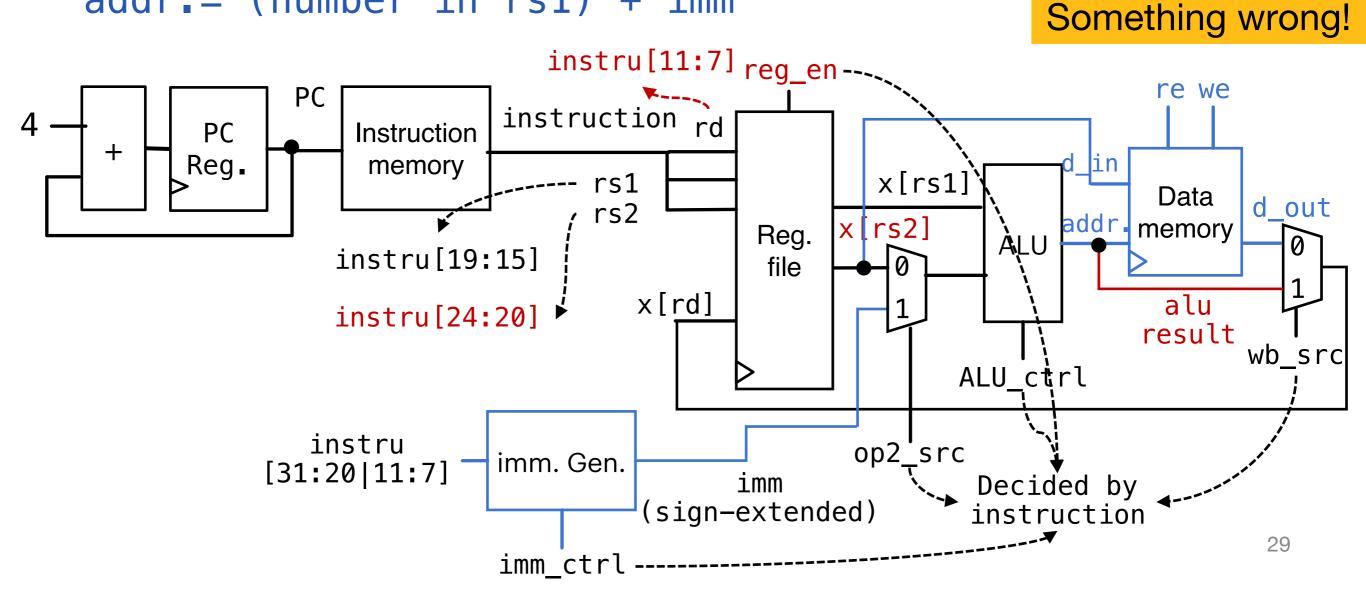

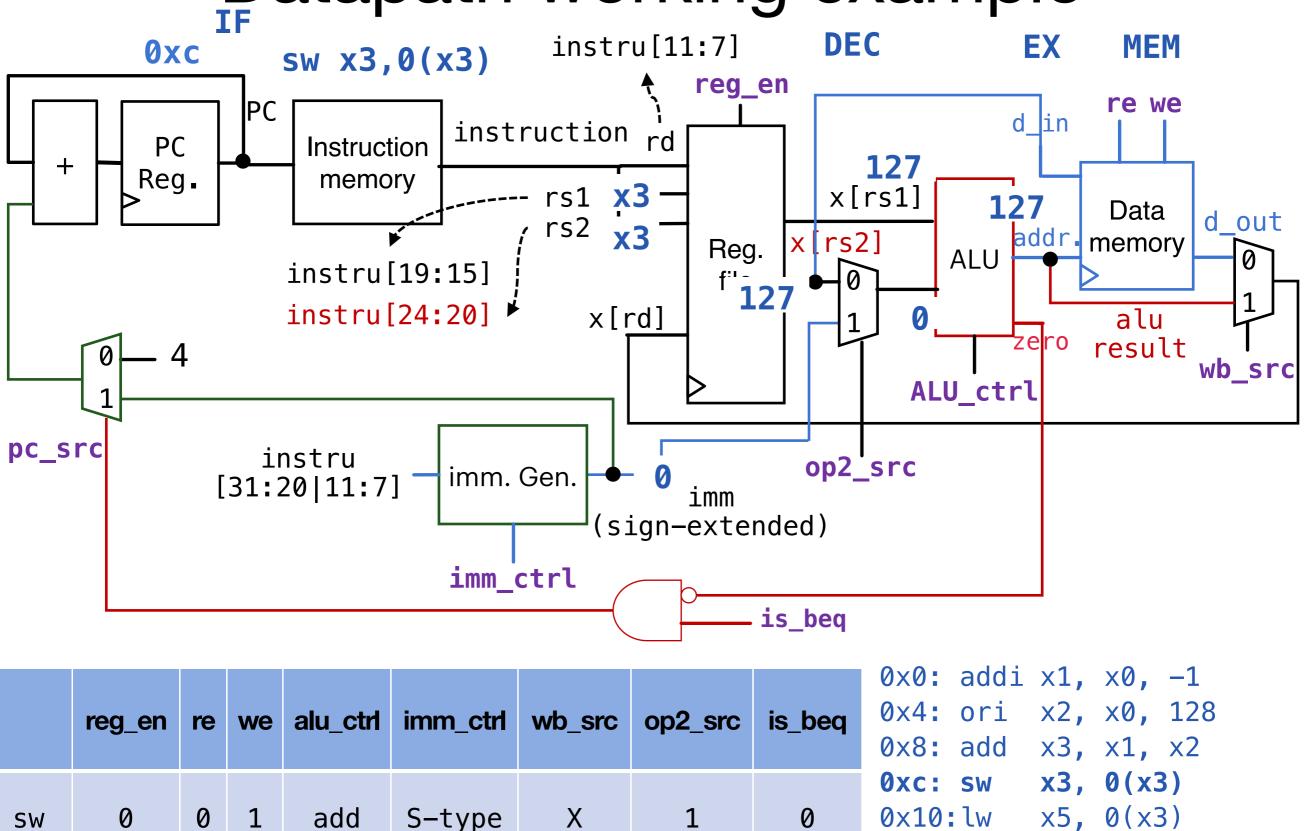

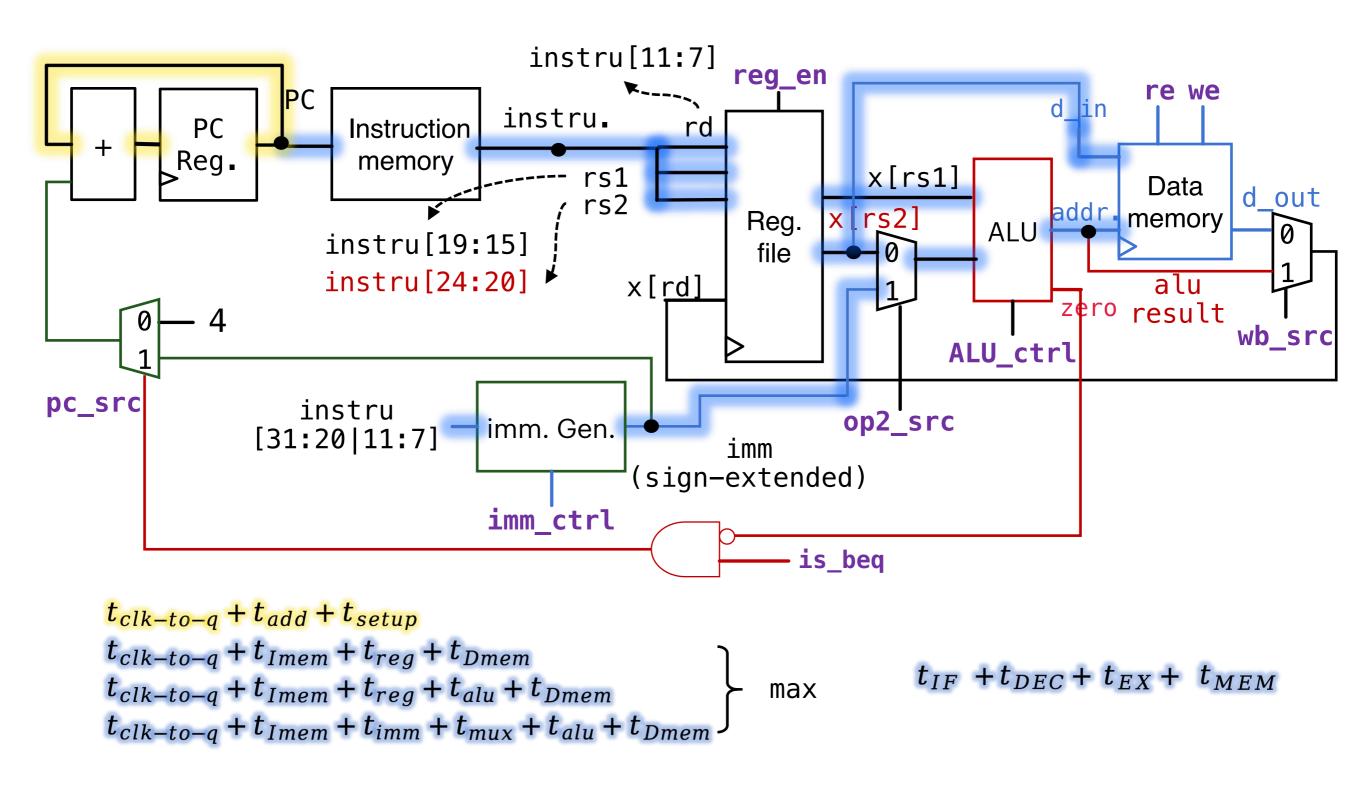

• sw rs2, imm(rs1): Store word at rs2 to memory addr. addr.= (number in rs1) + imm

• sw rs2, imm(rs1):Store word at rs2 to memory addr. addr.= (number in rs1) + imm

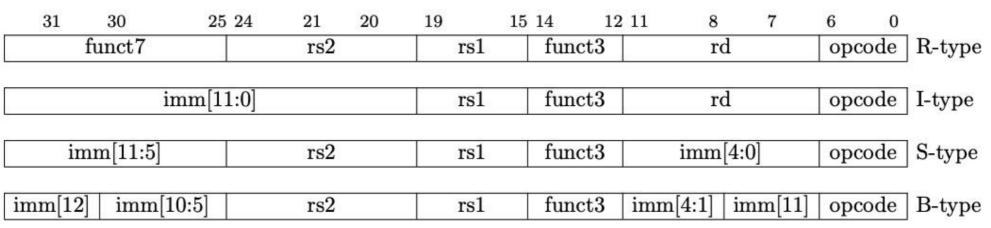

| Imm. Gen. |         |     |          |          |        |        |  |  |  |

|-----------|---------|-----|----------|----------|--------|--------|--|--|--|

| 31 2      | 5 24 20 | 19  | 15 14 12 | 2 11 7   | 6      | 0      |  |  |  |

| funct7    | rs2     | rs1 | funct3   | rd       | opcode | R-type |  |  |  |

|           |         |     |          |          |        |        |  |  |  |

| imm[11    | :0]     | rs1 | funct3   | rd       | opcode | I-type |  |  |  |

|           |         |     |          | 5        |        |        |  |  |  |

| imm[11:5] | rs2     | rs1 | funct3   | imm[4:0] | opcode | S-type |  |  |  |

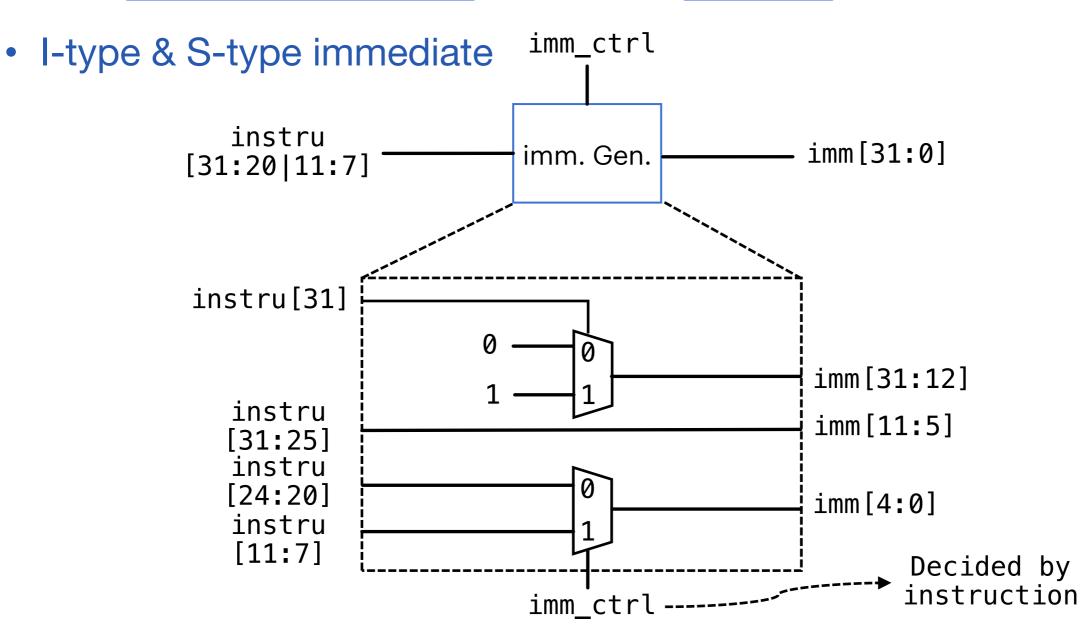

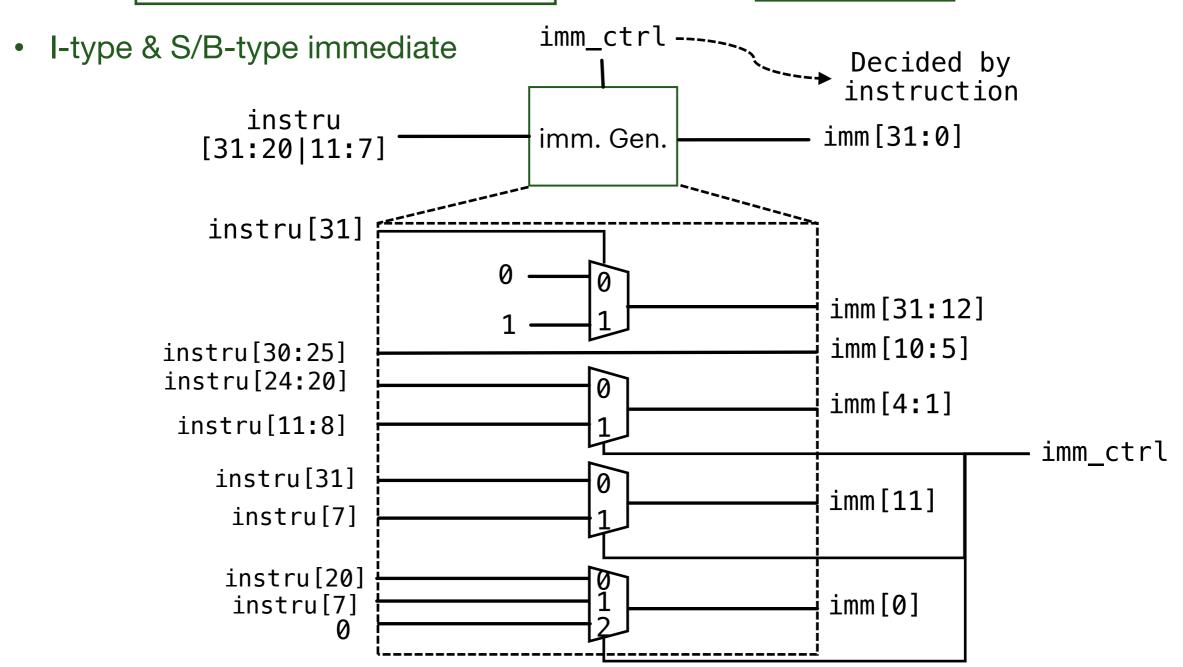

• I-type immediate

• sw rs2, imm(rs1): Store word at rs2 to memory addr. addr.= (number in rs1) + imm

## **Regfile modification**

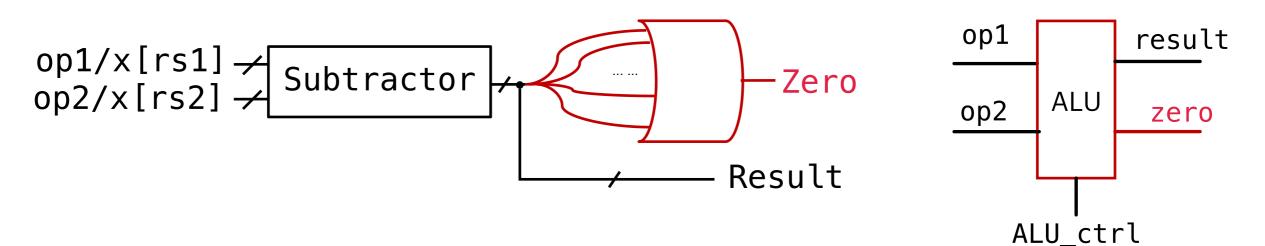

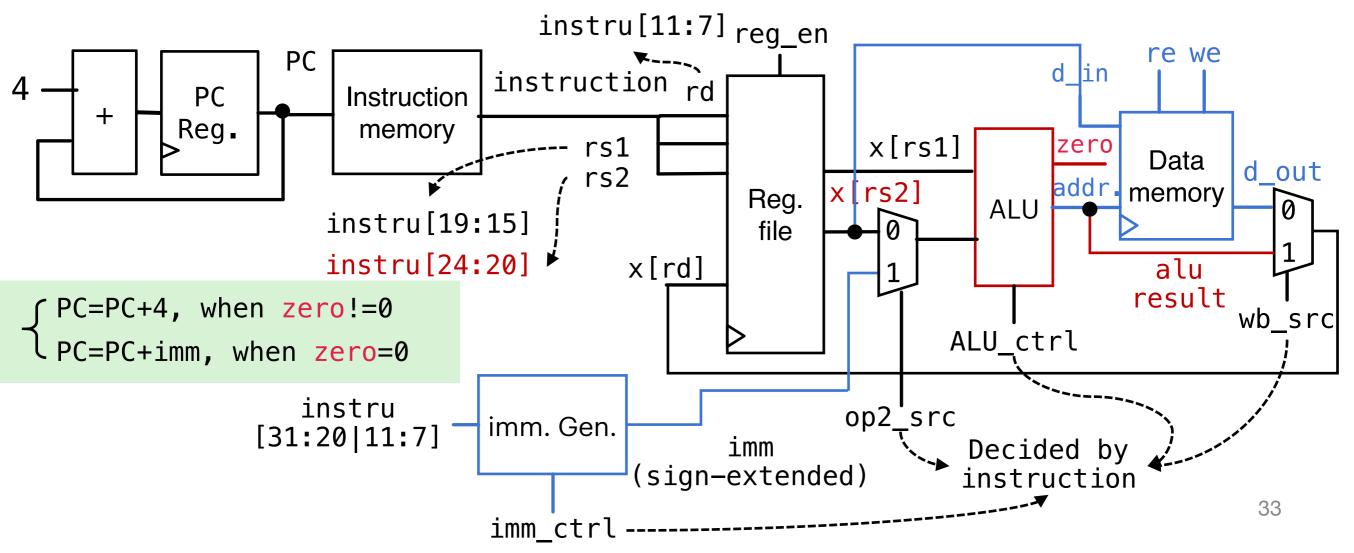

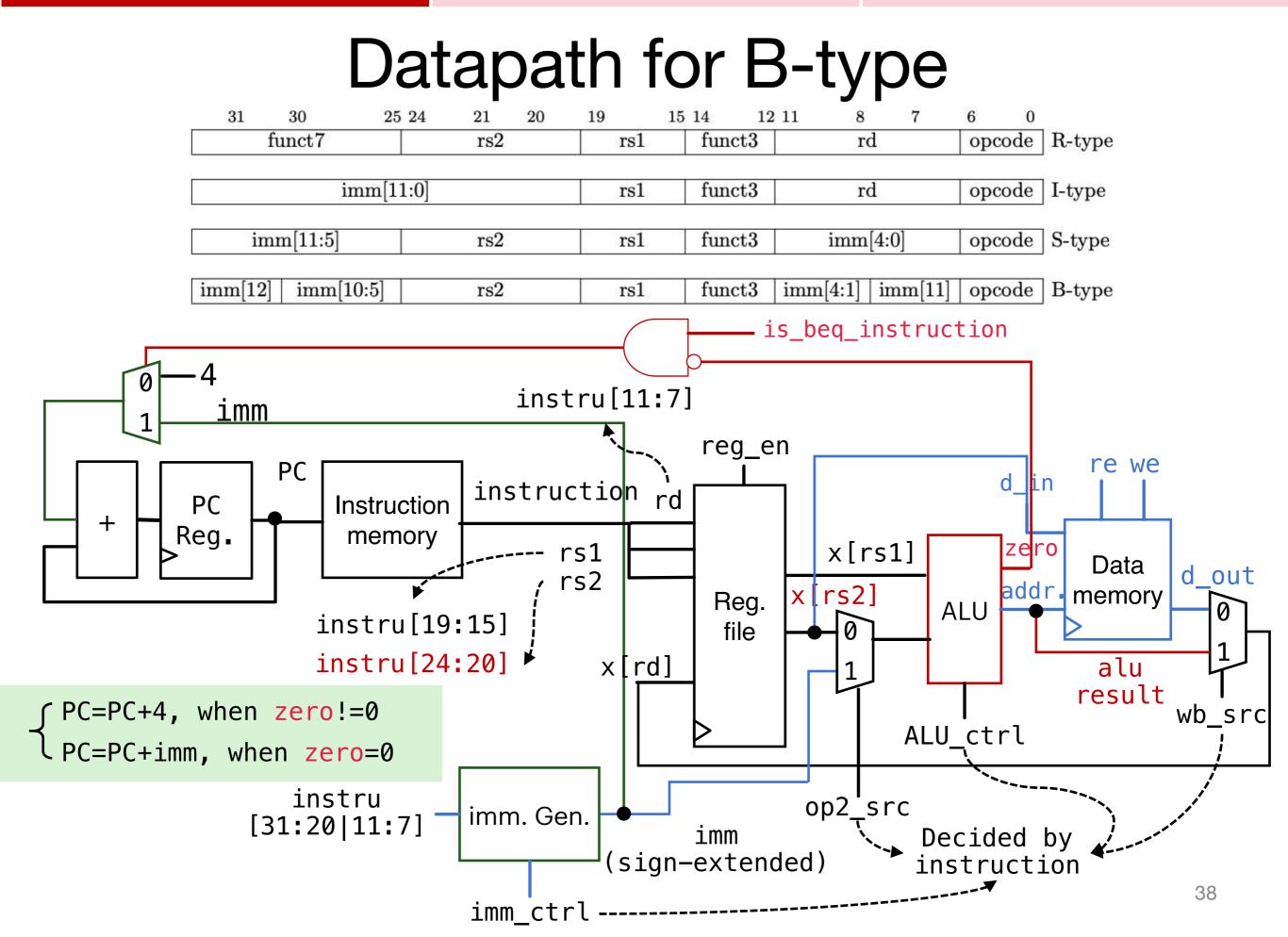

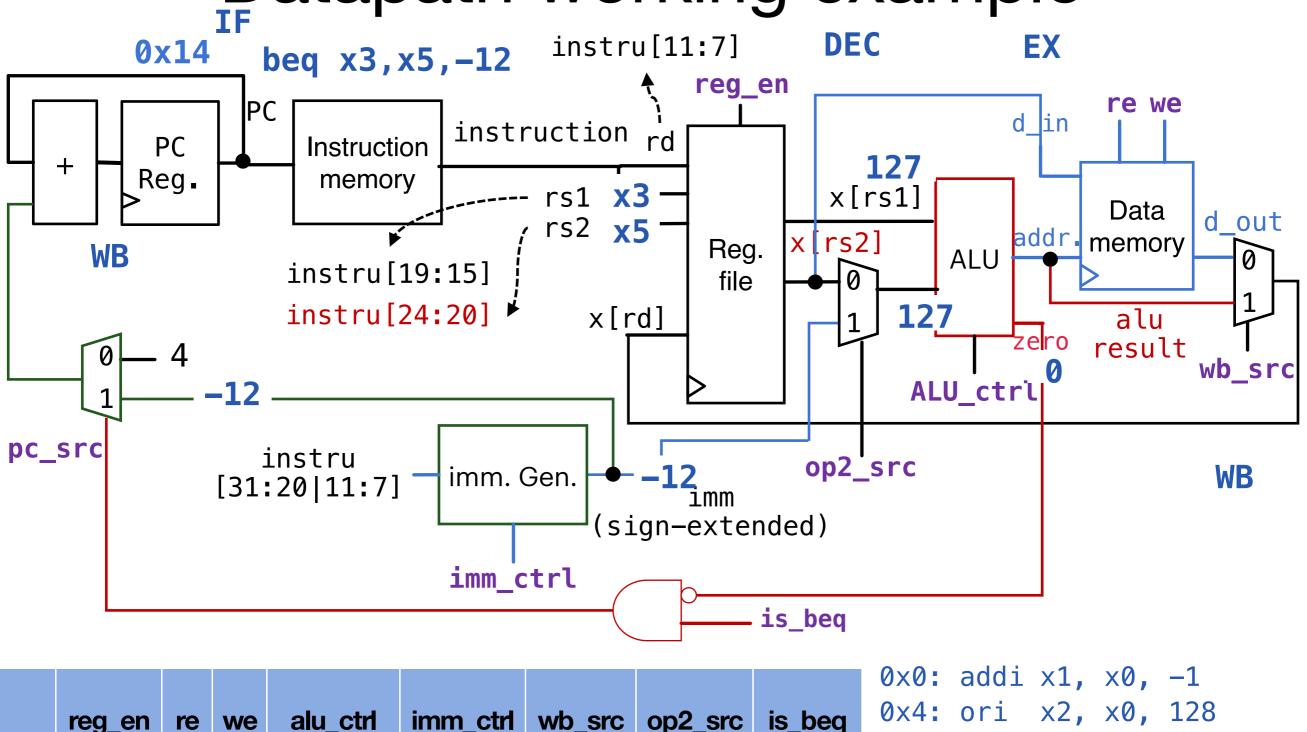

- beq rs1,rs2,L(imm/label)

- Go to label if x [rs1] == x [rs2]; otherwise, go to next statement

- beq rs1,rs2,L(imm/label)

- Go to label if x [rs1] == x [rs2]; otherwise, go to next statement

- Recall in ALU

$x[rs1] == x[rs2] \leftrightarrow x[rs1] - x[rs2] == 0$

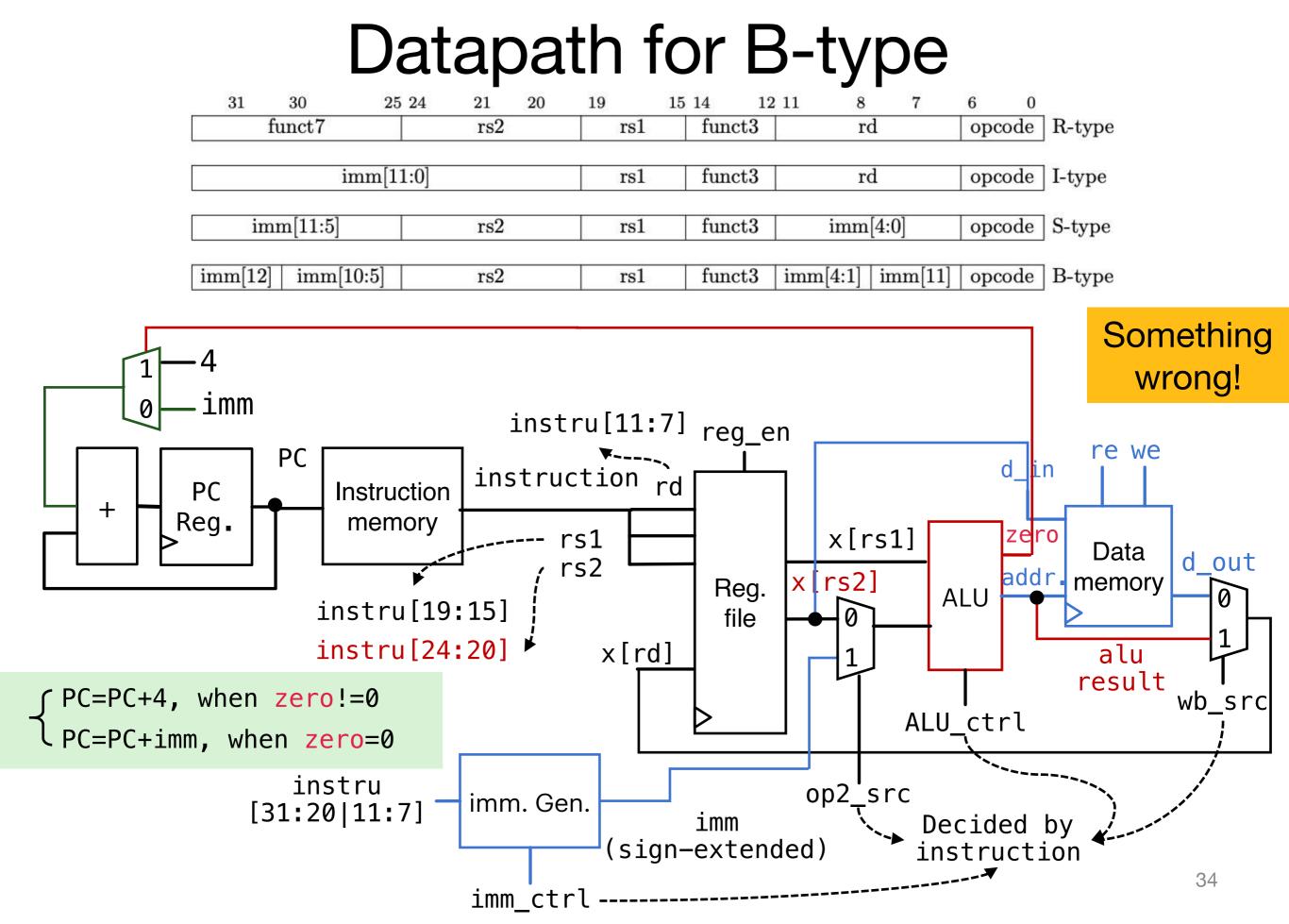

- beq rs1,rs2,L(imm/label)

- Go to label if x [rs1] == x [rs2]; otherwise, go to next instruction

is\_beq\_instruction

Recall beq

| imm[12 10:5]        | rs2     | rs1        | 000 | imm[4:1 11] | 1100011 | BEQ |  |  |  |

|---------------------|---------|------------|-----|-------------|---------|-----|--|--|--|

| Truth table         |         |            |     |             |         |     |  |  |  |

| Inst                | tru[14: | is_beq_ins |     |             |         |     |  |  |  |

| (                   | 000 110 | 1          |     |             |         |     |  |  |  |

| All the other cases |         |            |     | 0           |         |     |  |  |  |

is\_beq\_instruction=i[14]i[13]i[12]i[6]i[5]i[4]i[3]i[2]i[1]i[0]

|   | 31     | 30                               | 25    | 24   | 21  | 20 | 19  | 15 14 | $12 \ 11$ | 8                       | 7       | 6    | 0  |            |

|---|--------|----------------------------------|-------|------|-----|----|-----|-------|-----------|-------------------------|---------|------|----|------------|

|   |        | funct7                           |       |      | rs2 |    | rs1 | func  | et3       | $\mathbf{rd}$           |         | opco | de | R-type     |

|   |        |                                  |       |      |     |    | 7   |       |           |                         |         | 1    |    |            |

| _ |        | in                               | nm[1] | 1:0] |     |    | rs1 | func  | et3       | rd                      |         | opco | de | I-type     |

|   |        | [4.4. 8]                         |       |      |     |    |     |       |           |                         | <u></u> |      |    | <b>a</b> . |

|   | iı     | nm[11:5]                         |       |      | rs2 |    | rs1 | func  | et3       | $\operatorname{imm}[4:$ | 0]      | opco | de | S-type     |

|   | [10    | 1                                | 0 =1  |      |     |    | _   | C     |           | [4 4] .                 | [1 1]   |      | 1  | D          |

| 1 | mm[12] | $2] \mid \operatorname{imm}[10]$ | 0:5]  |      | rs2 |    | rs1 | func  | et3 imn   | n[4:1]   ir             | nm[11]  | opco | de | B-type     |

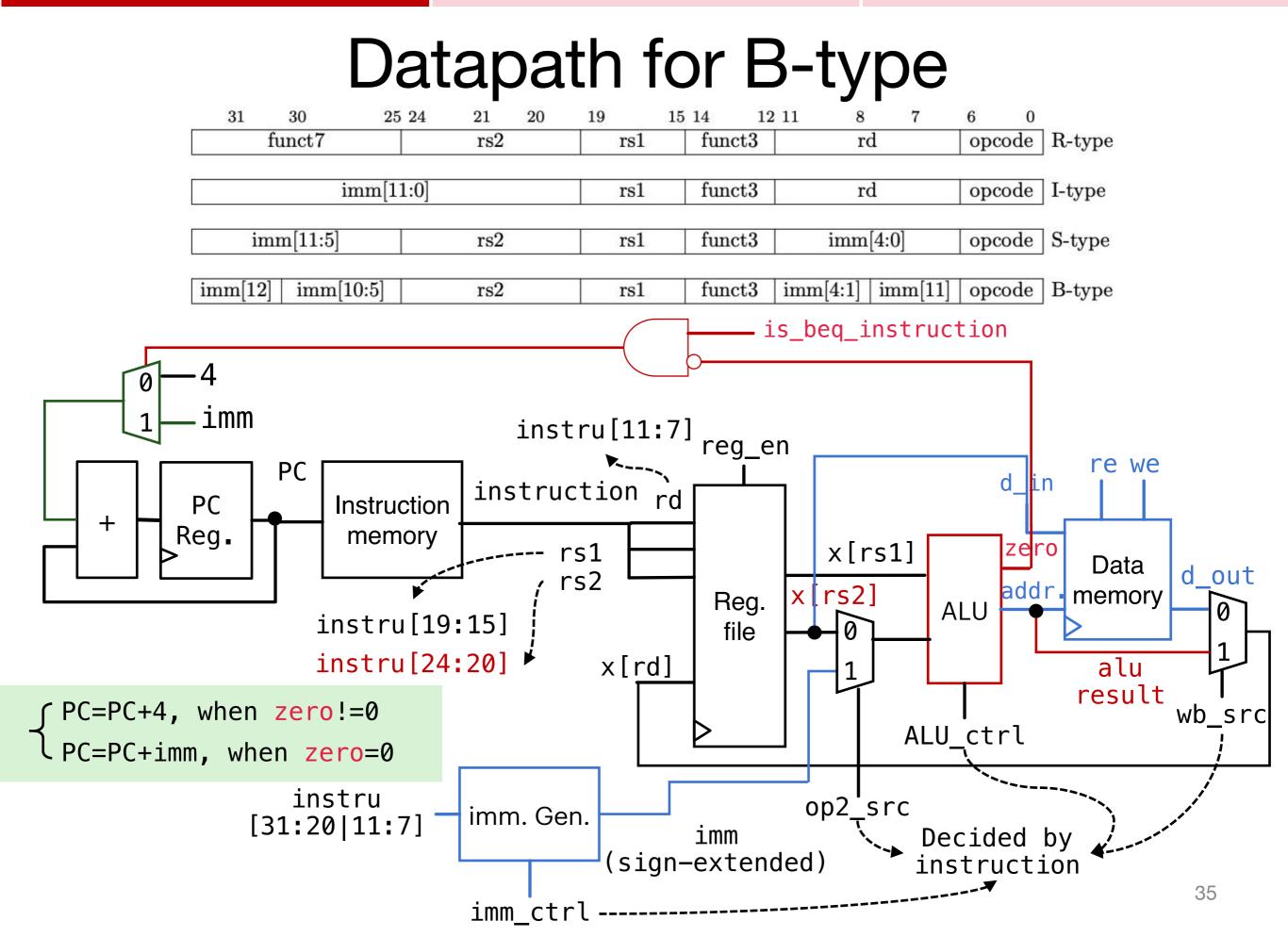

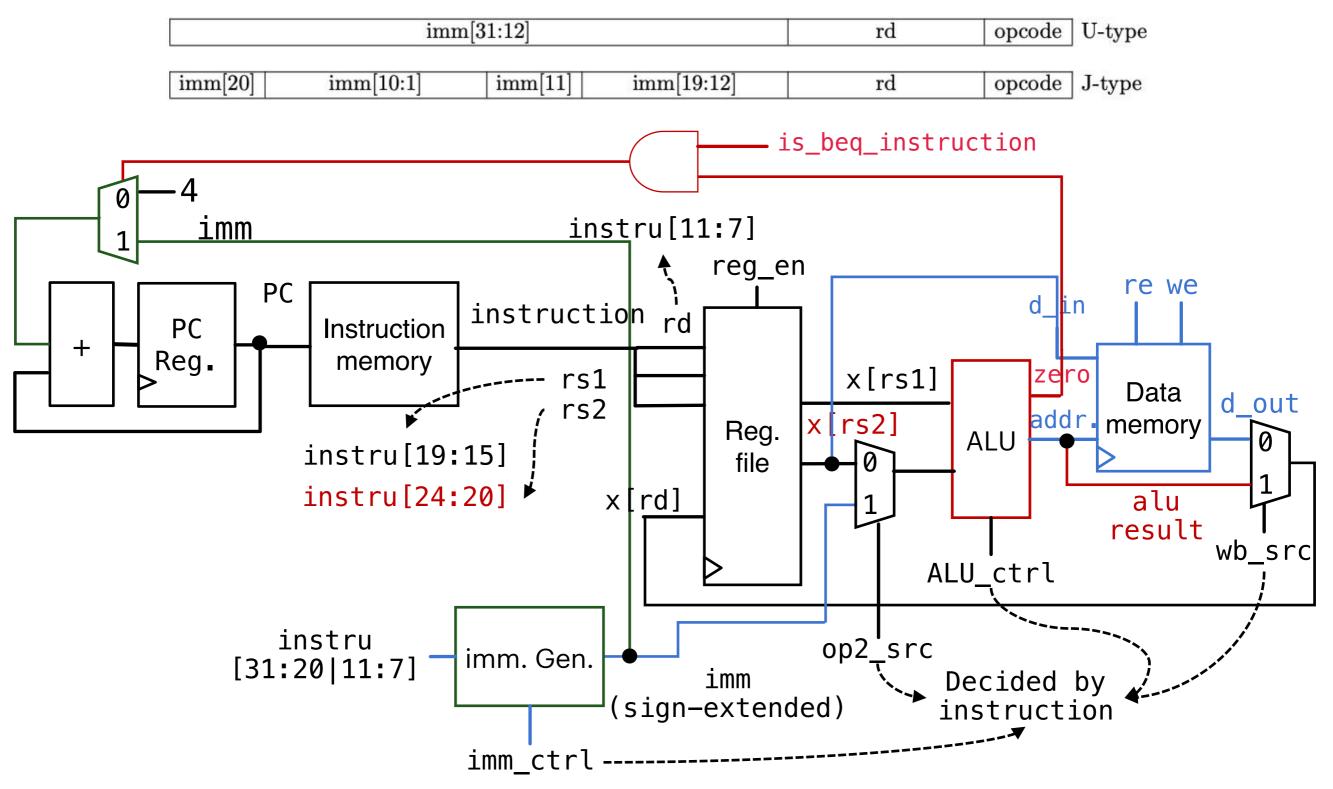

#### Datapath for the other types

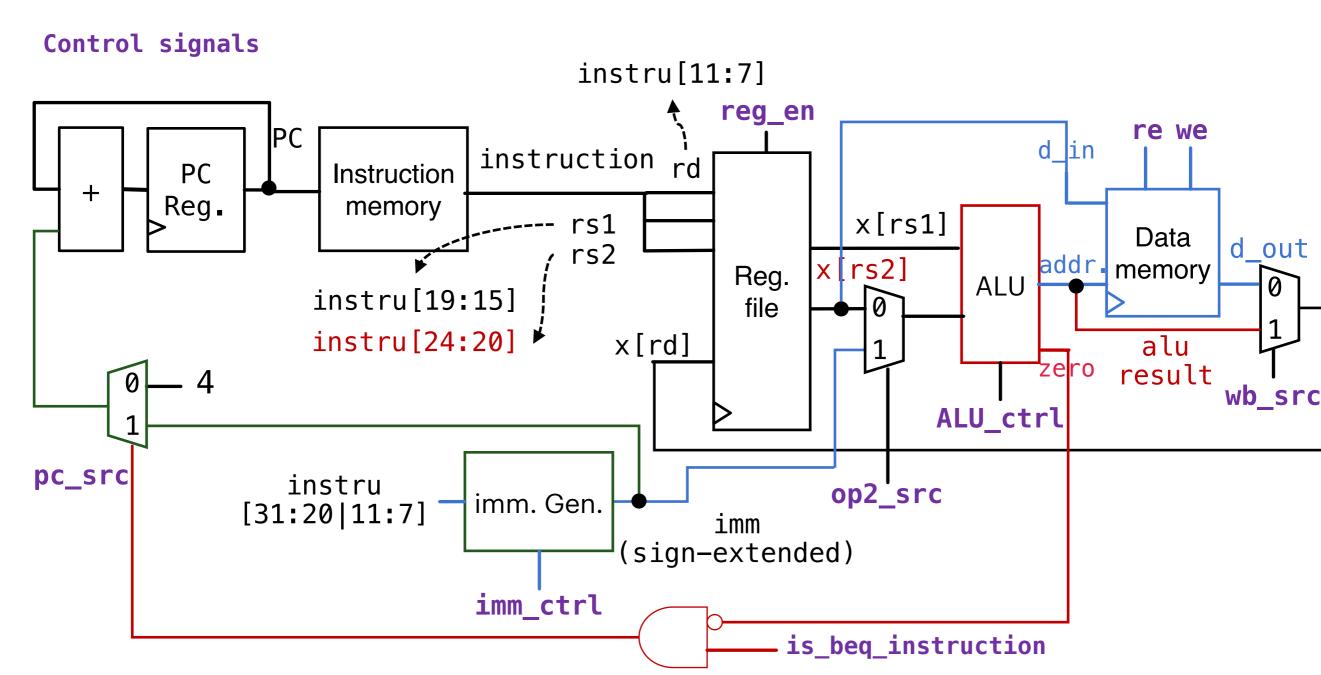

#### Control signals

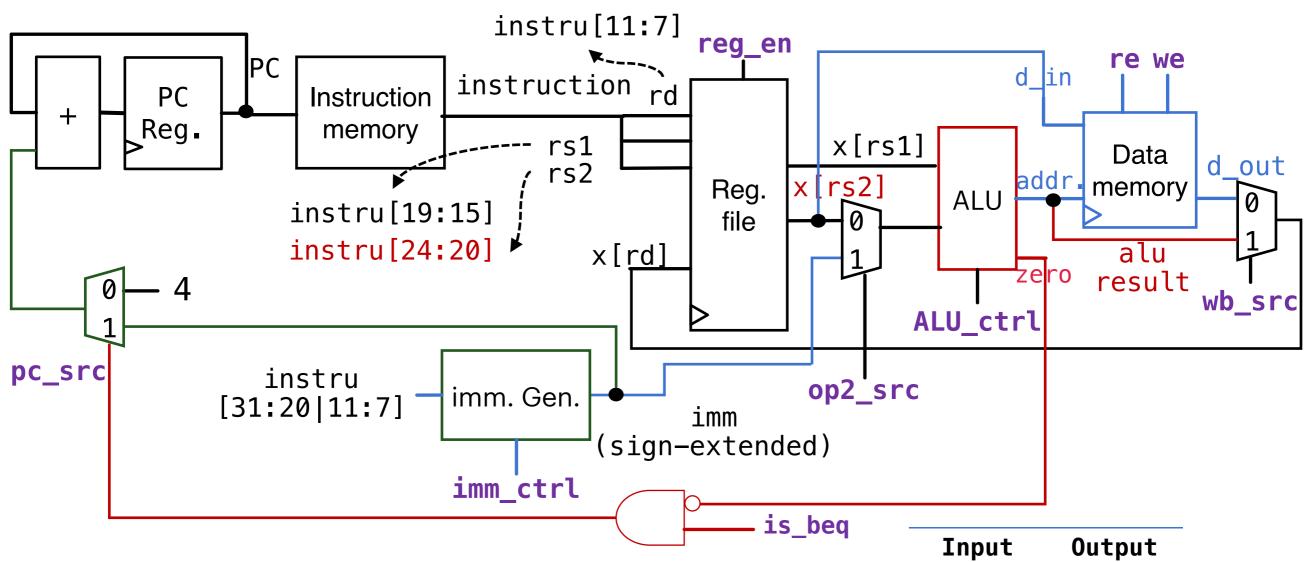

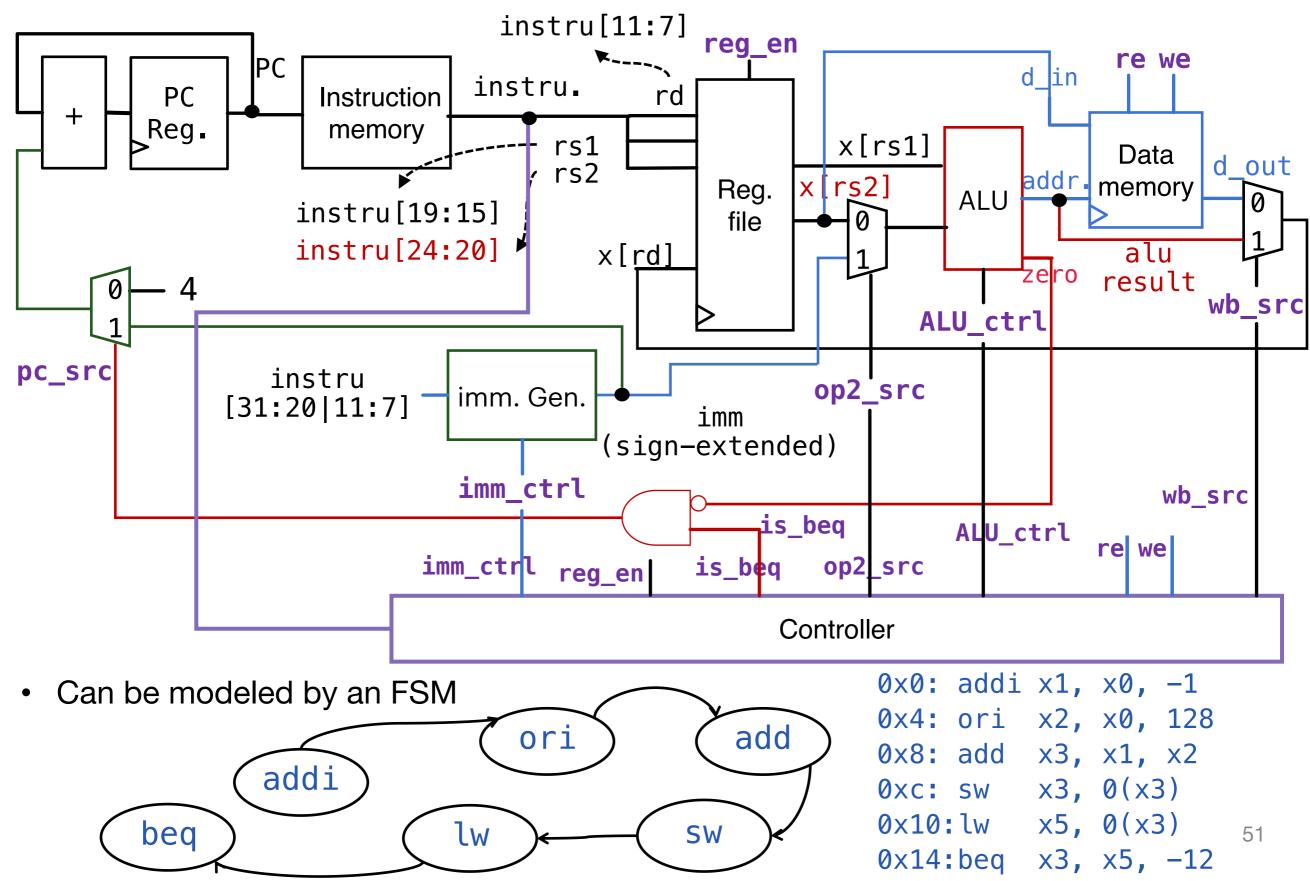

This is a datapath that supports R-type & I-type arithmetic and logic operations, lw, sw and beq

addi

1

0

0

add

I-type

0x10:lw x5, 0(x3)

0x14:beq x3, x5, -12 41

0

1

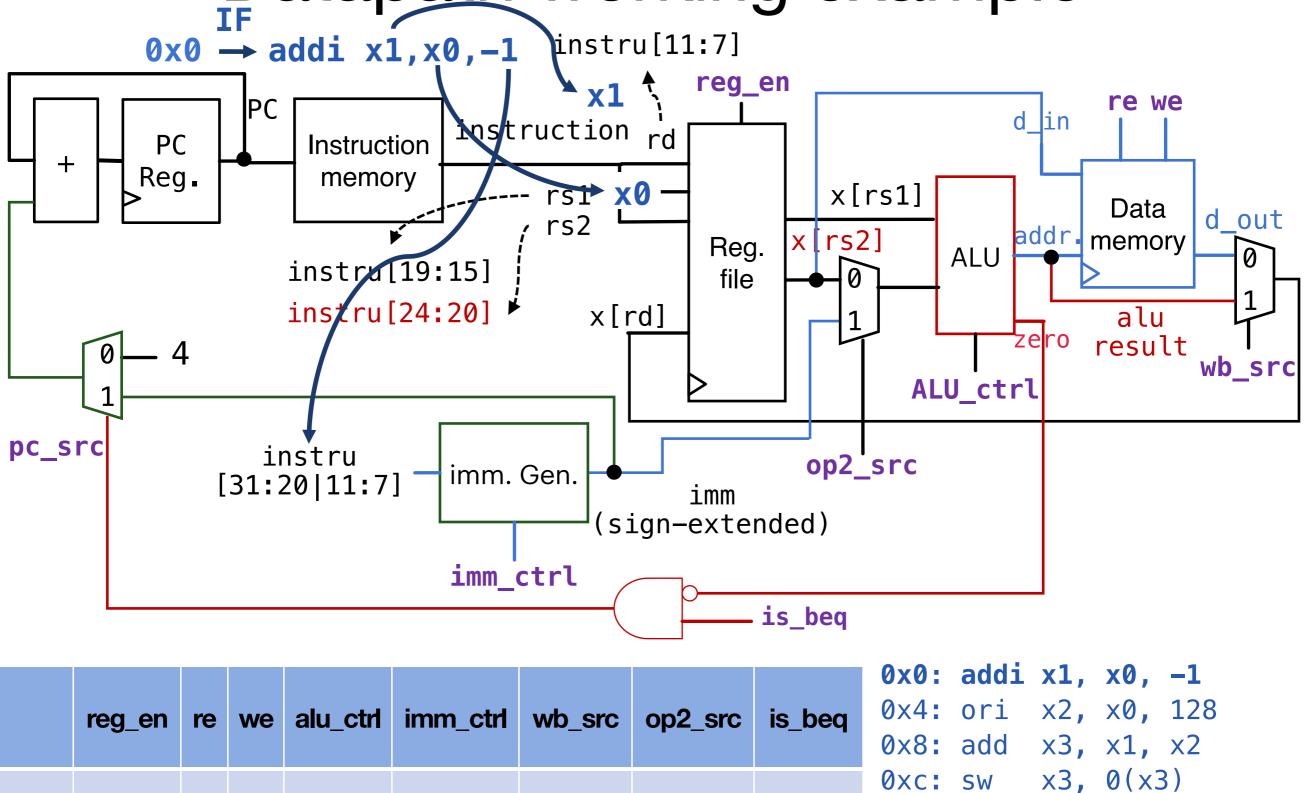

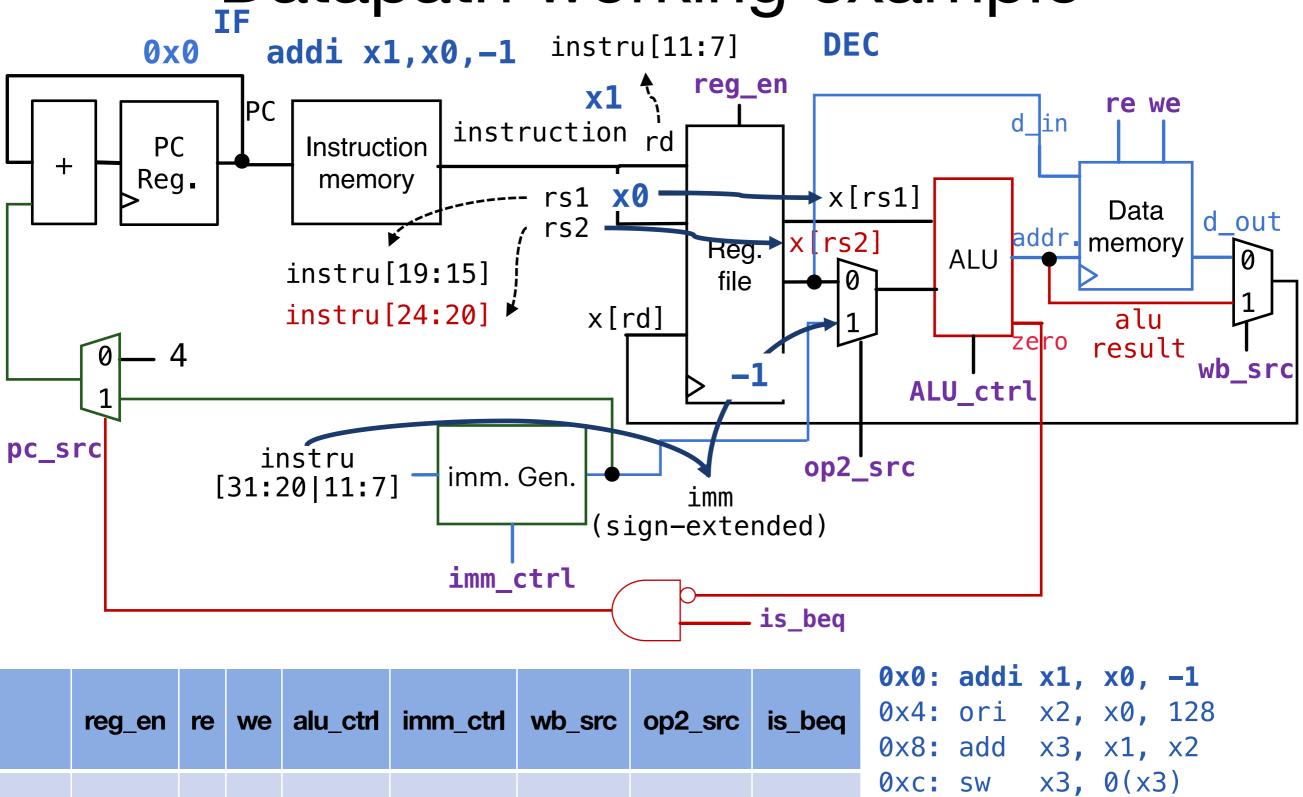

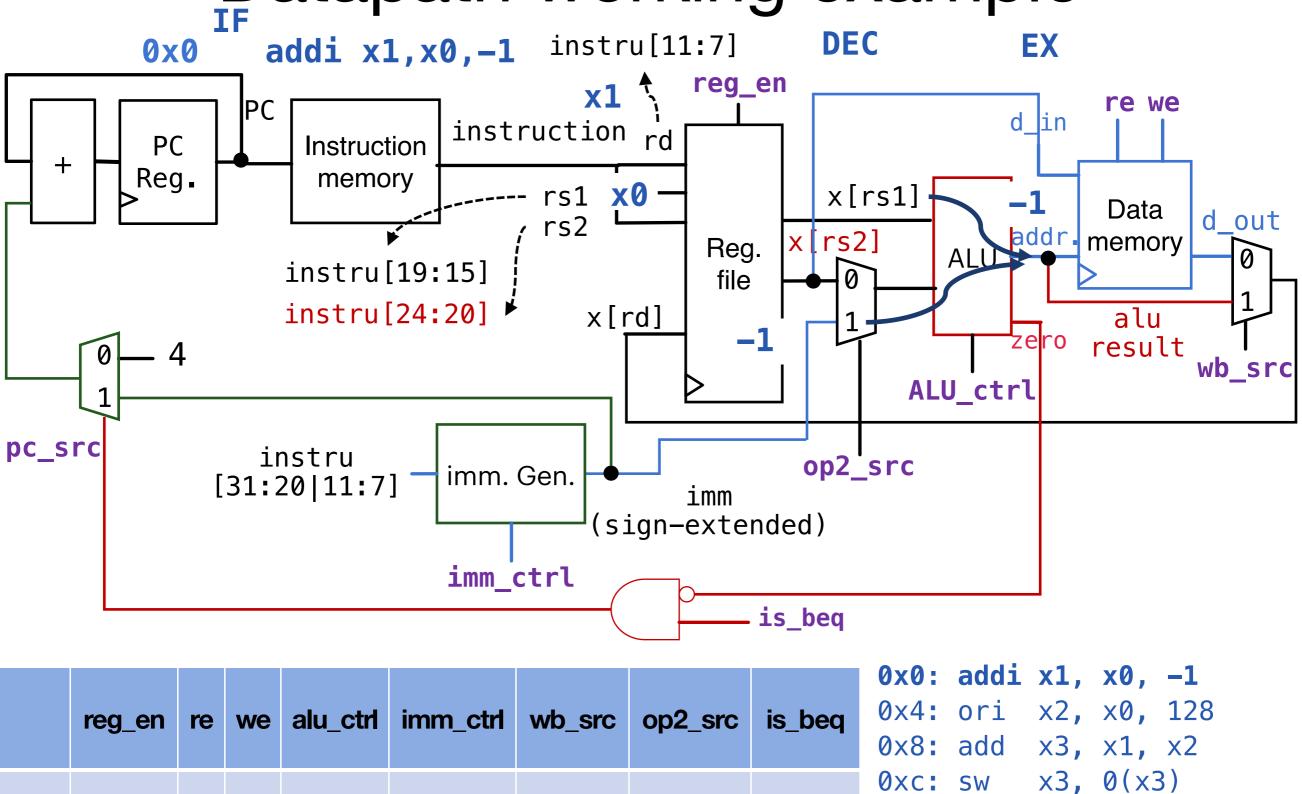

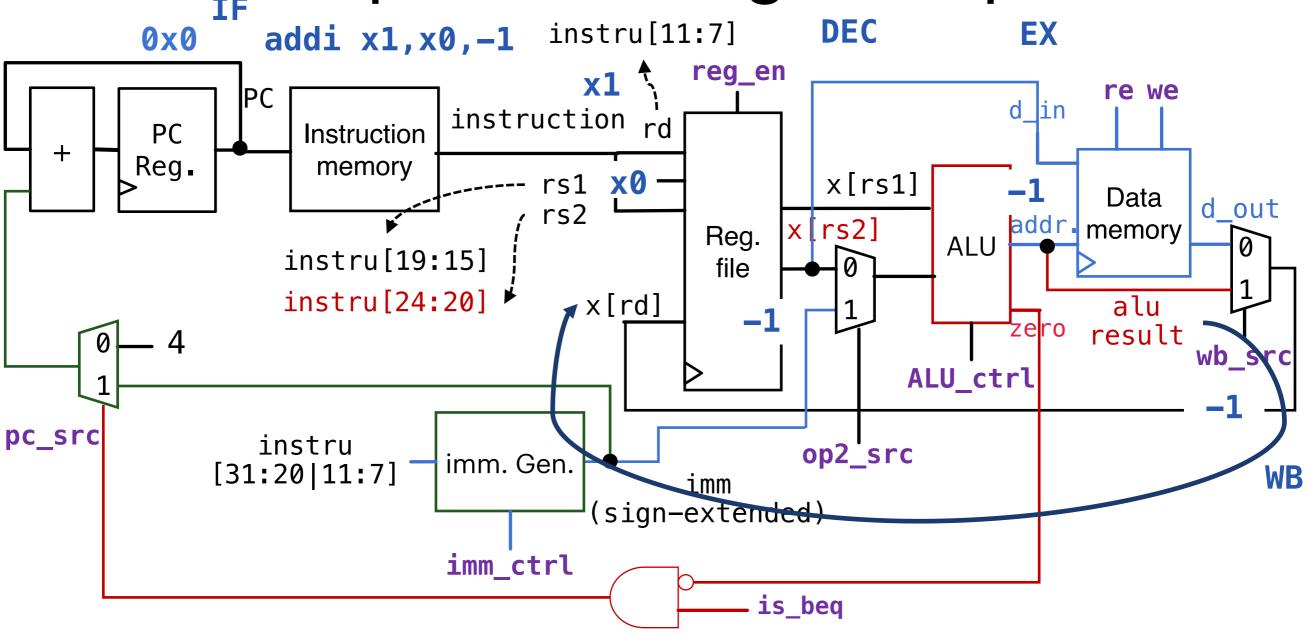

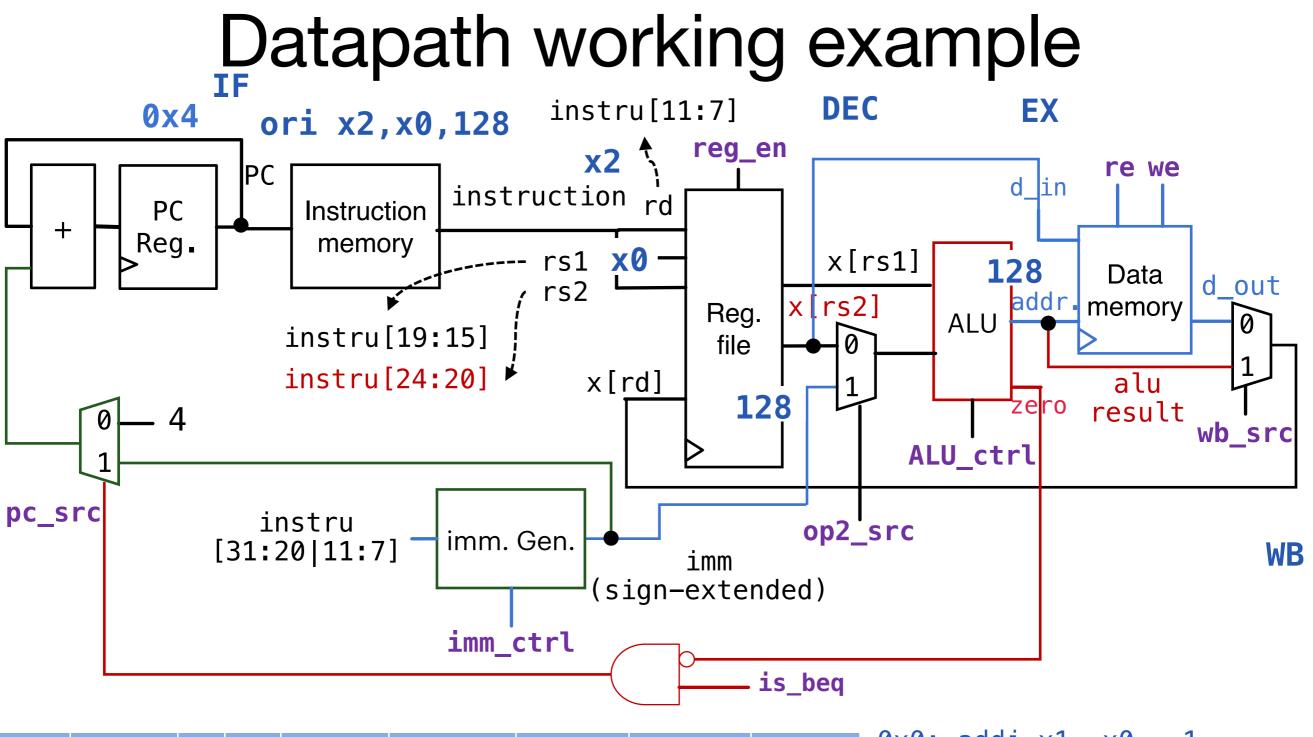

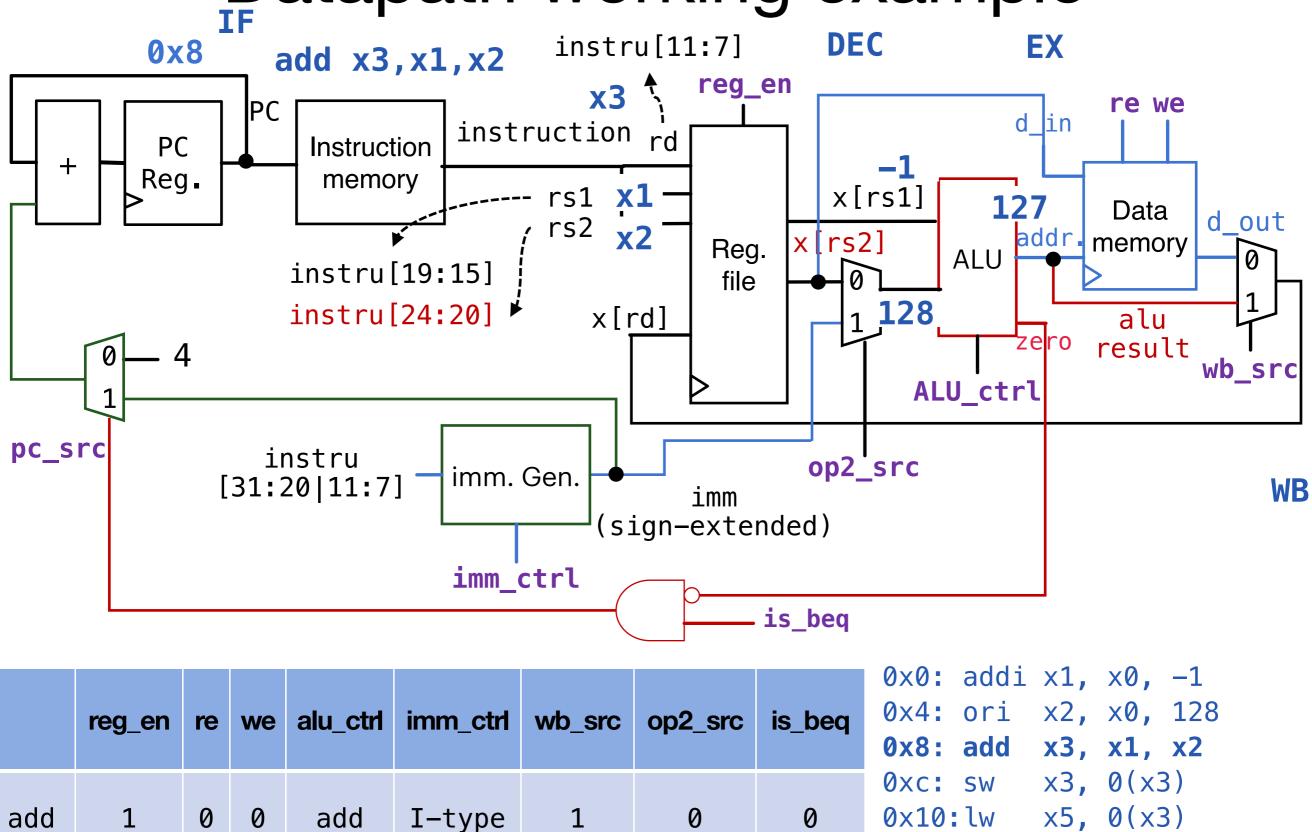

### Datapath working example

1

addi

1

0

0

add

I-type

1

0x10:lw x5, 0(x3)

0x14:beg x3, x5, -12 42

0

1

addi

1

0

0

add

I-type

1

1

0

0x10:lw x5, 0(x3)

0x14:beg x3, x5, -12 43

|      |            |    |    |          |          |        |         |        | 0x0: a | ddi > | <b>x1</b> , | x0,          | -1            |

|------|------------|----|----|----------|----------|--------|---------|--------|--------|-------|-------------|--------------|---------------|

|      | rea en     | re | we | alu ctrl | imm_ctrl | wb src | op2 src | is bea | 0x4: o | ri >  | ×2,         | x0,          | 128           |

|      | <b>9</b> _ |    |    |          |          |        |         |        | 0x8: a | ndd > | x3,         | x1,          | x2            |

|      |            |    |    |          |          |        |         |        | 0xc: s | w >   | κ3,         | <b>0(</b> x3 | 3)            |

| addi | 1          | 0  | 0  | add      | I-type   | 1      | 1       | 0      | 0x10:l | W >   | ×5,         | 0(x3         | 3)            |

|      |            |    |    |          |          |        |         |        | 0x14:b | eq >  | x3,         | x5,          | <b>-12</b> 44 |

|     | reg_en | re | we | alu_ctrl | imm_ctrl | wb_src | op2_src | is_beq | <b>0x4: ori</b><br>0x8: add | ×1, ×0, -1<br><b>x2, x0, 128</b><br>×3, ×1, ×2 |

|-----|--------|----|----|----------|----------|--------|---------|--------|-----------------------------|------------------------------------------------|

| ori | 1      | 0  | 0  | or       | I-type   | 1      | 1       | 0      | 0x10:lw                     | x3, 0(x3)<br>x5, 0(x3)<br>x3, x5, -12 45       |

0x14:beg x3, x5, -12 46

0x14:beg x3, x5, -12 47

0x14:beg x3, x5, -12 48

|     | reg_en | re | we | alu_ctrl | imm_ctrl | wb_src | op2_src | is_beq |         | x2, x0, 128<br>x3, x1, x2                |

|-----|--------|----|----|----------|----------|--------|---------|--------|---------|------------------------------------------|

| beq | 0      | 0  | 0  | sub      | B-type   | Х      | 0       |        | 0x10:lw | x3, 0(x3)<br>x5, 0(x3)<br>x3, x5, -12 49 |

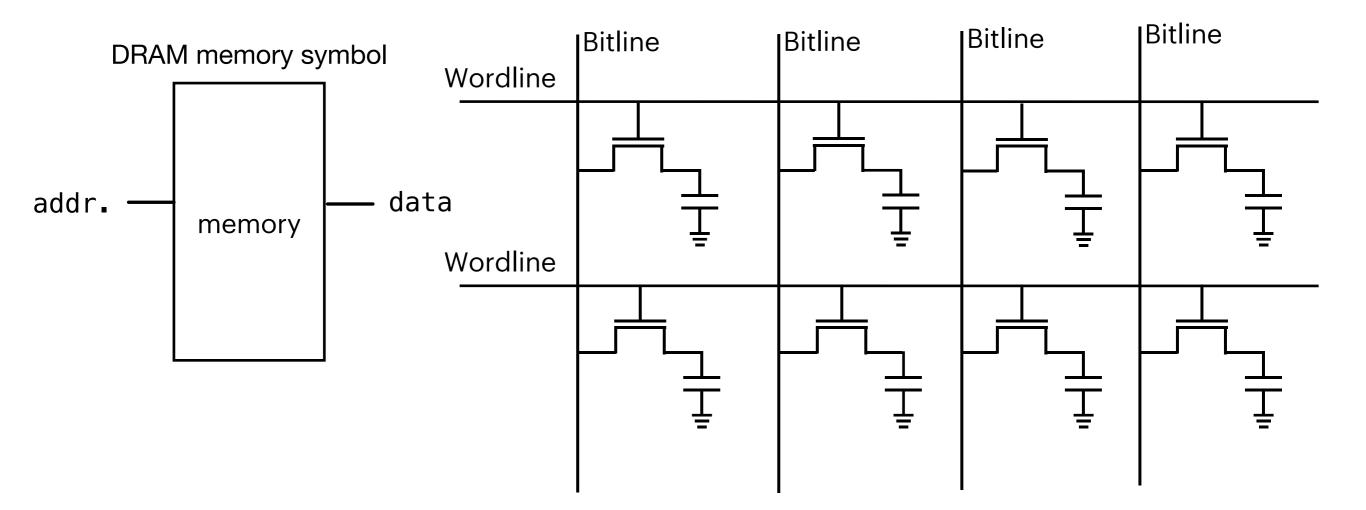

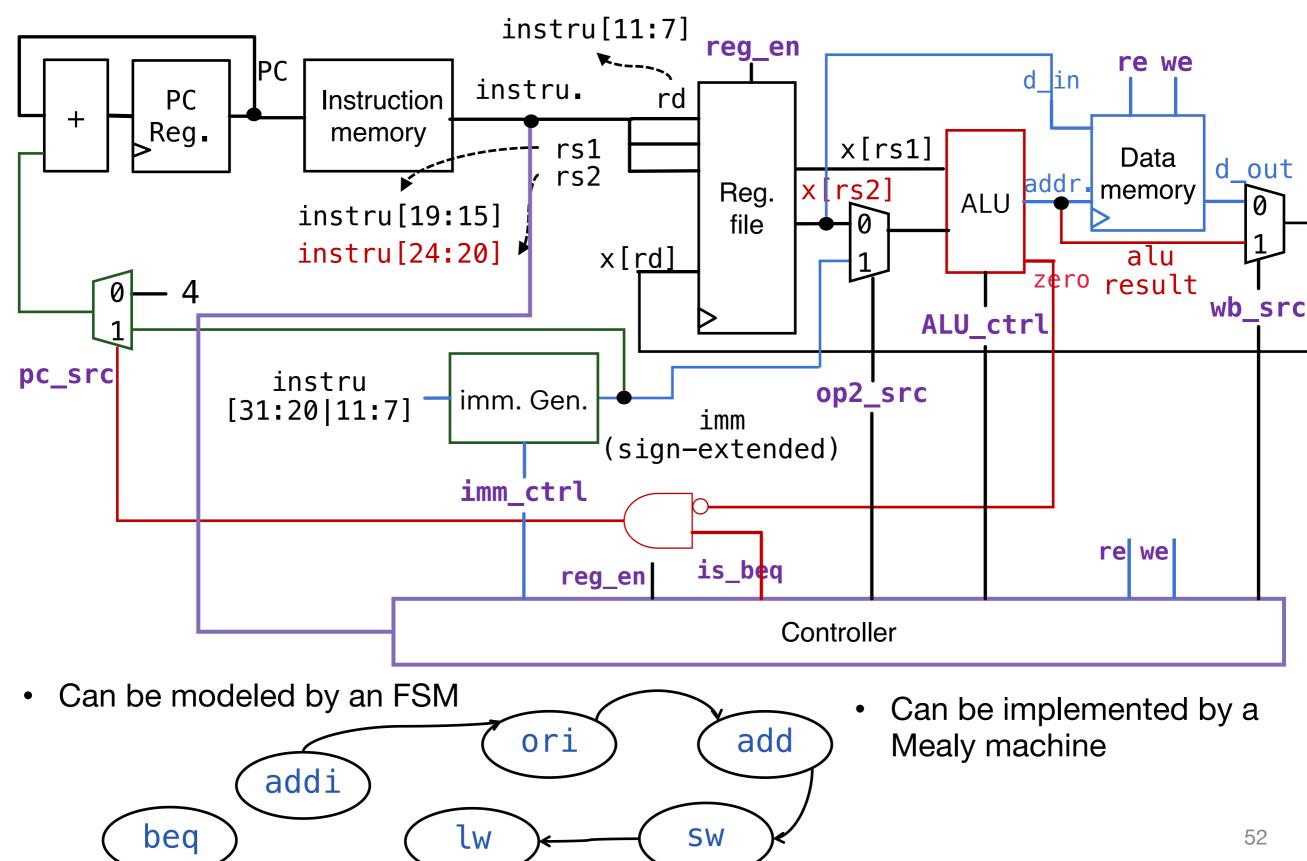

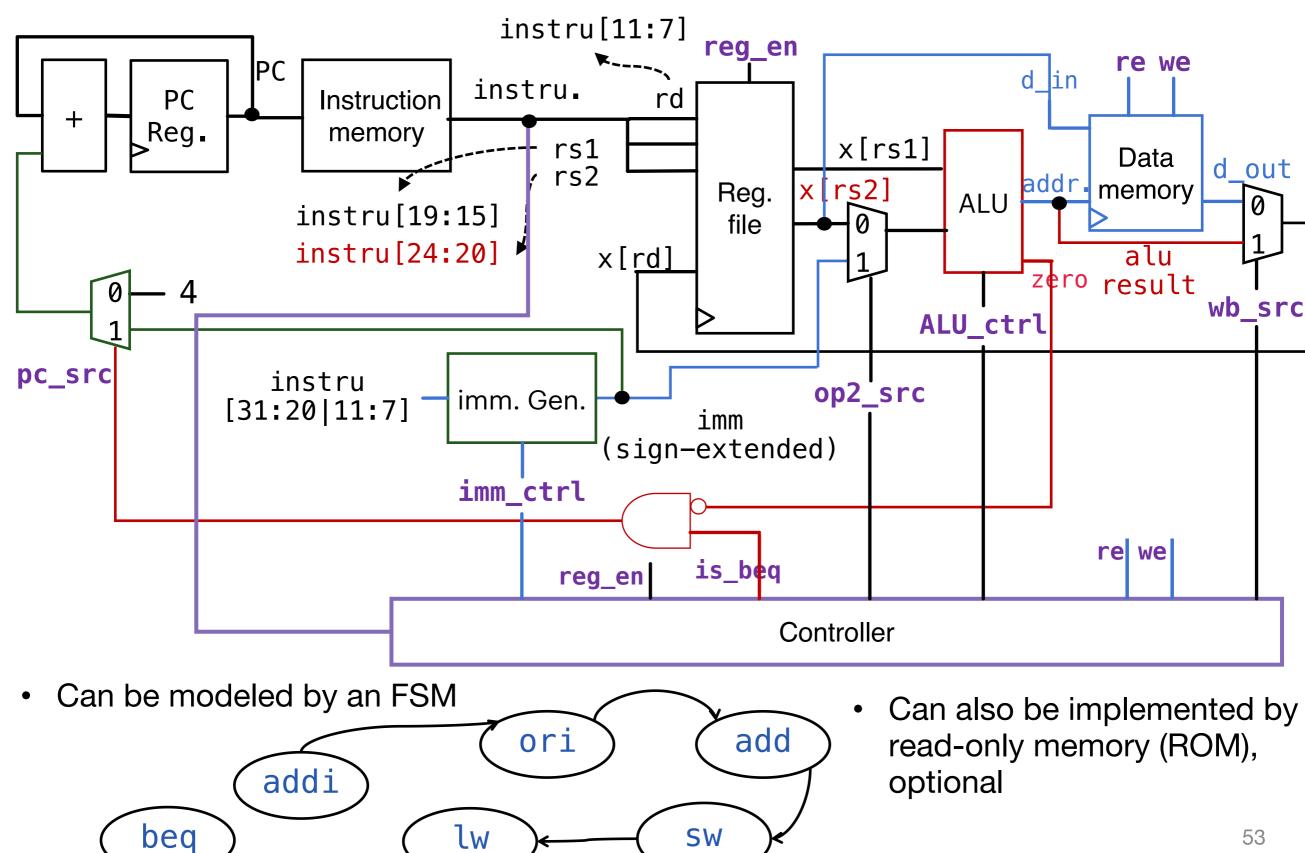

Datapath

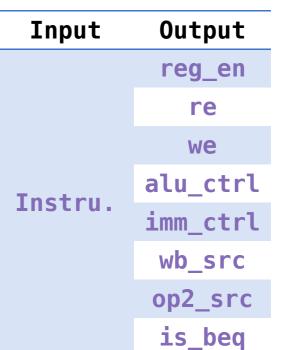

- Generate control signals guiding the datapath to execute instructions

- The inputs are instructions, the outputs are the control signals

- Once the type of instruction is determined, the control signal is determined

Datapath

Controller

Datapath

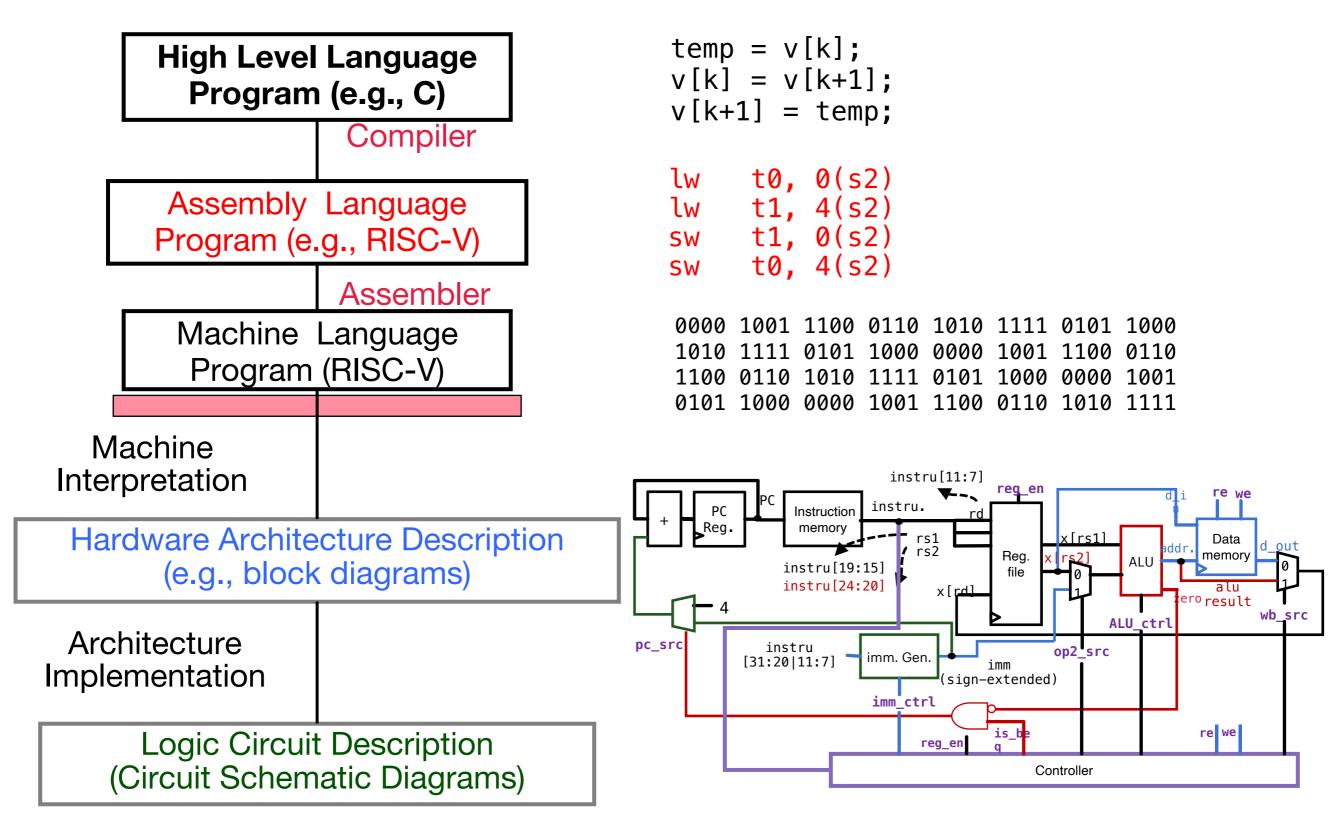

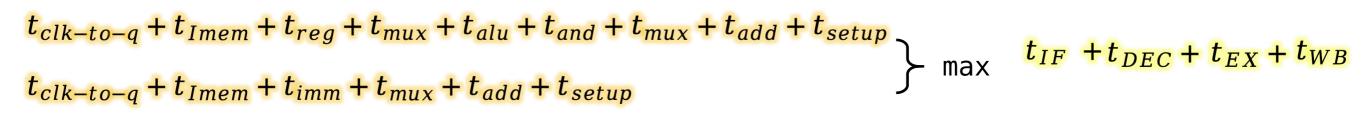

### Full stack explained

$t_{clk-to-q} + t_{add} + t_{setup}$

$t_{clk-to-q} + t_{Imem} + t_{reg} + t_{alu} + t_{mux} + t_{setup}$   $t_{clk-to-q} + t_{Imem} + t_{imm} + t_{mux} + t_{alu} + t_{mux} + t_{setup}$  I-type arithmetic & logic datapath

S-type datapath

B-type datapath

# Summary

- We have built a single-cycle CPU

- It supports R-type, I-type arithmetic & logic and load (lw), S-type sw and beq

- Datapath and controller are built seperately

- Different instruction activates different parts or steps/stages (IF/DEC/EXE/MEM/WB) of the datapath, thus has different delays. The longest delay (critical path) is used to estimate maximum frequency

- Nearly no CPU uses single-cycle design today.